#### High-level development and debugging of FPGA-based network programs

#### nik.sultana@cl.cam.ac.uk

Pietro Bressana, Richard Clegg, Paolo Costa, Jon Crowcroft, Salvator Galea, David Greaves, Luo Mai, Andrew W Moore, Richard Mortier, Peter Pietzuch, Jonny Shipton, Robert Soule, Nik Sultana, Marcin Wojcik, Noa Zilberman

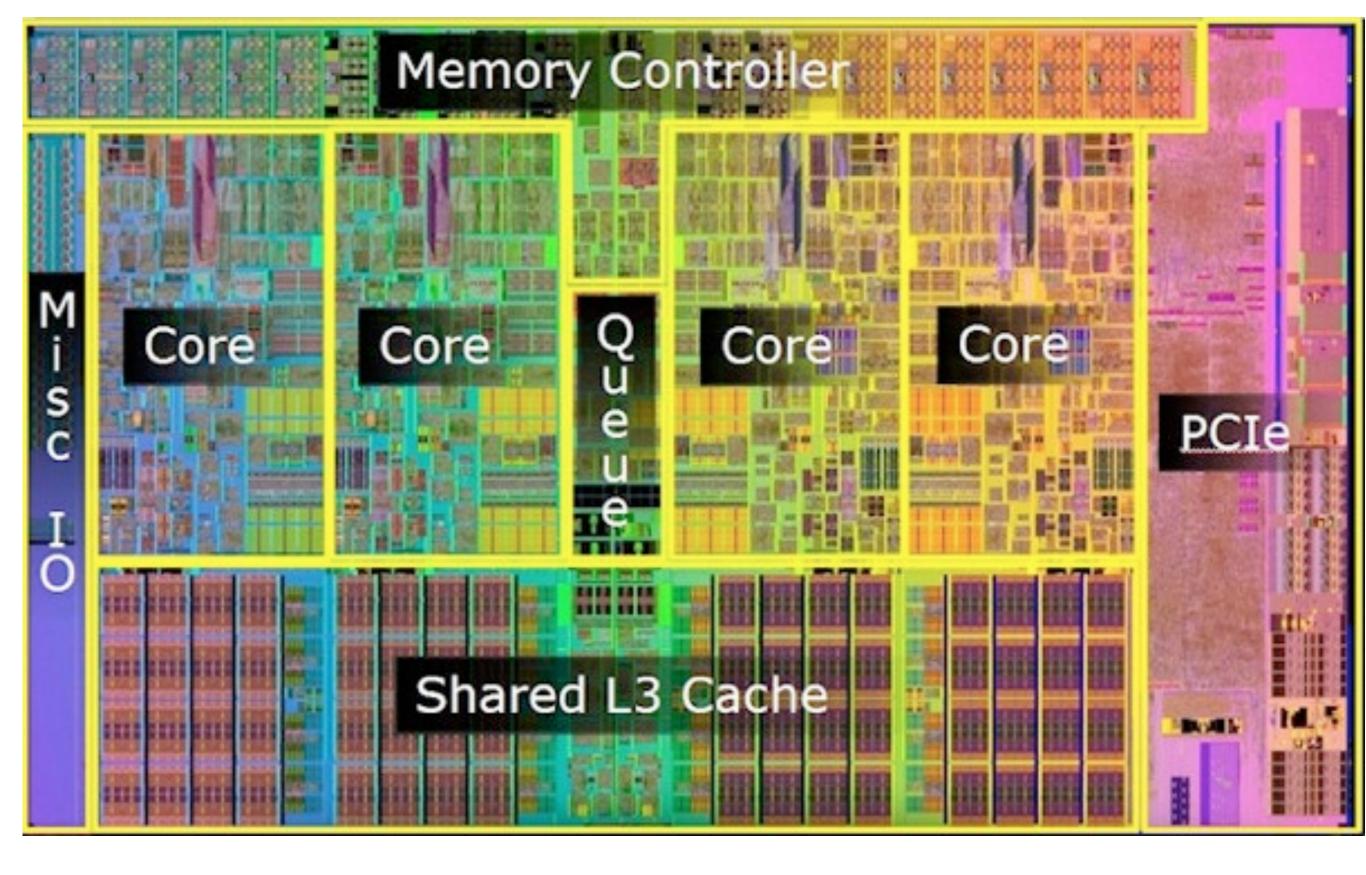

Intel Lynnfield (c) Intel

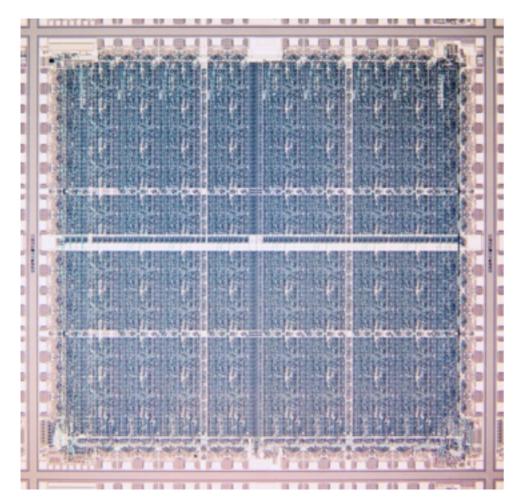

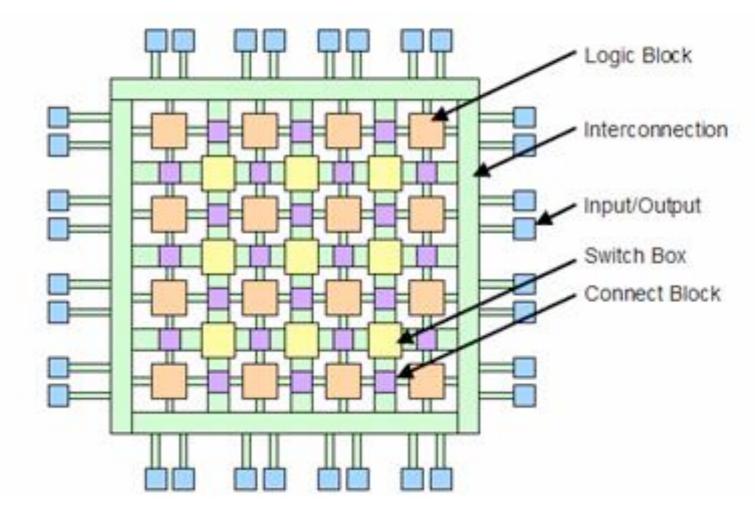

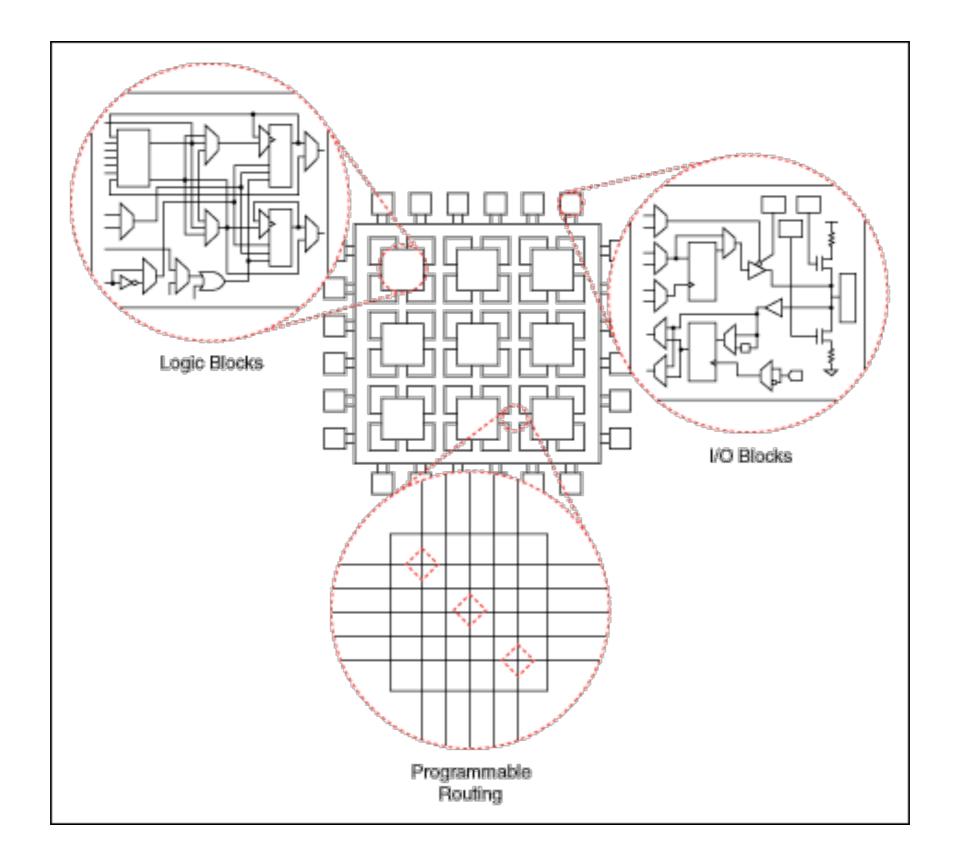

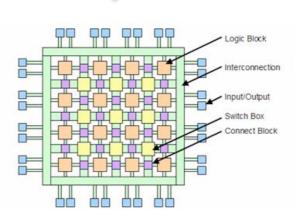

# Field-programmable gate arrays

http://ca.olin.edu/2005/fpga\_dsp/fpga.html

Xilinx XC2064 FPGA 64 CLB x (2 3-LUTs + FF) (c) Xilinx

http://zone.ni.com/reference/en-XX/help/371599J-01/lvfpgaconcepts/fpga\_basic\_chip\_terms/

- FPGAs becoming more **powerful** and **prevalent**.

Most recently in datacentres.

- oe.g., Azure, Baidu, Amazon.

- FPGAs becoming more **powerful** and **prevalent**.

Most recently in datacentres.

- But still **difficult** to program and debug!

To both hardware and non-hardware people.

#### Both technical and non-technical difficulties.

OHardware programming unlike software programming.

OGenerating a bitstream is a lengthy process.

O Differing interpretations for standard HDLs.

O Quality of the tools is less polished than for software.

O Strong vendor bias, closed formats, hold things back.

- FPGAs becoming more **powerful** and **prevalent**.

Most recently in datacentres.

- But still difficult to program and debug!

To both hardware and non-hardware people.

Both technical and non-technical difficulties.

- 30+ years of research into using high-level languages for circuit description. 20+ years commercial tooling (Synopsys Behavoural Compiler in 1994)

- FPGAs becoming more **powerful** and **prevalent**.

Most recently in datacentres.

- But still difficult to program and debug!

To both hardware and non-hardware people.

Both technical and non-technical difficulties.

- 30+ years of research into using high-level languages for circuit description. 20+ years commercial tooling (Synopsys Behavoural Compiler in 1994)

- Experience has been mixed you can't be everything to everybody! But lots of progress.

#### High-level development and debugging of FPGA-based network programs

#### High-level development and debugging of FPGA-based network programs

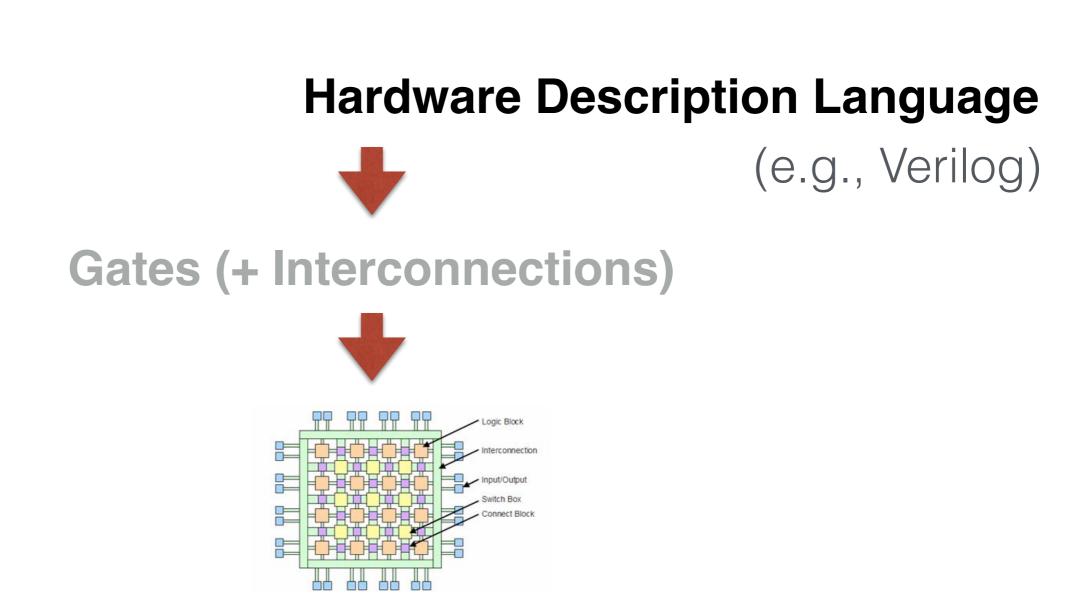

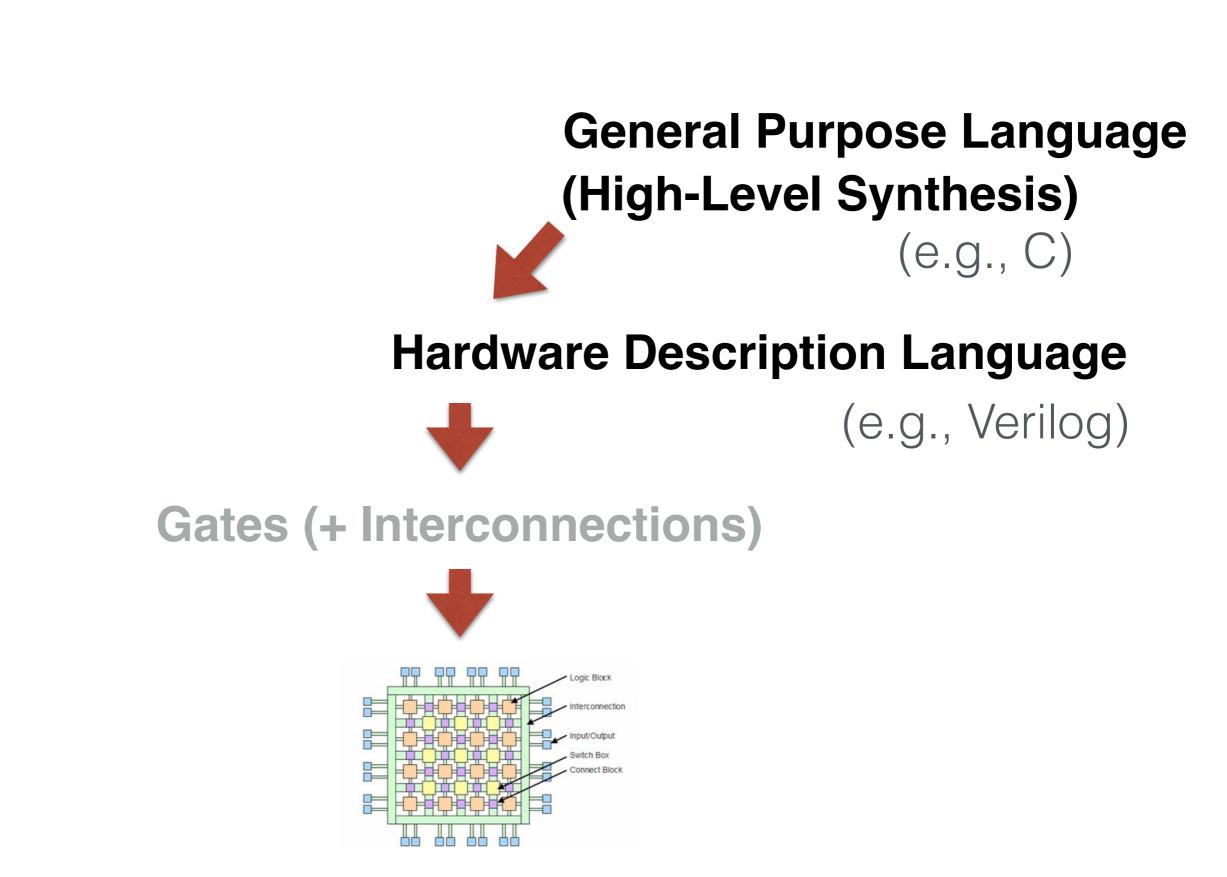

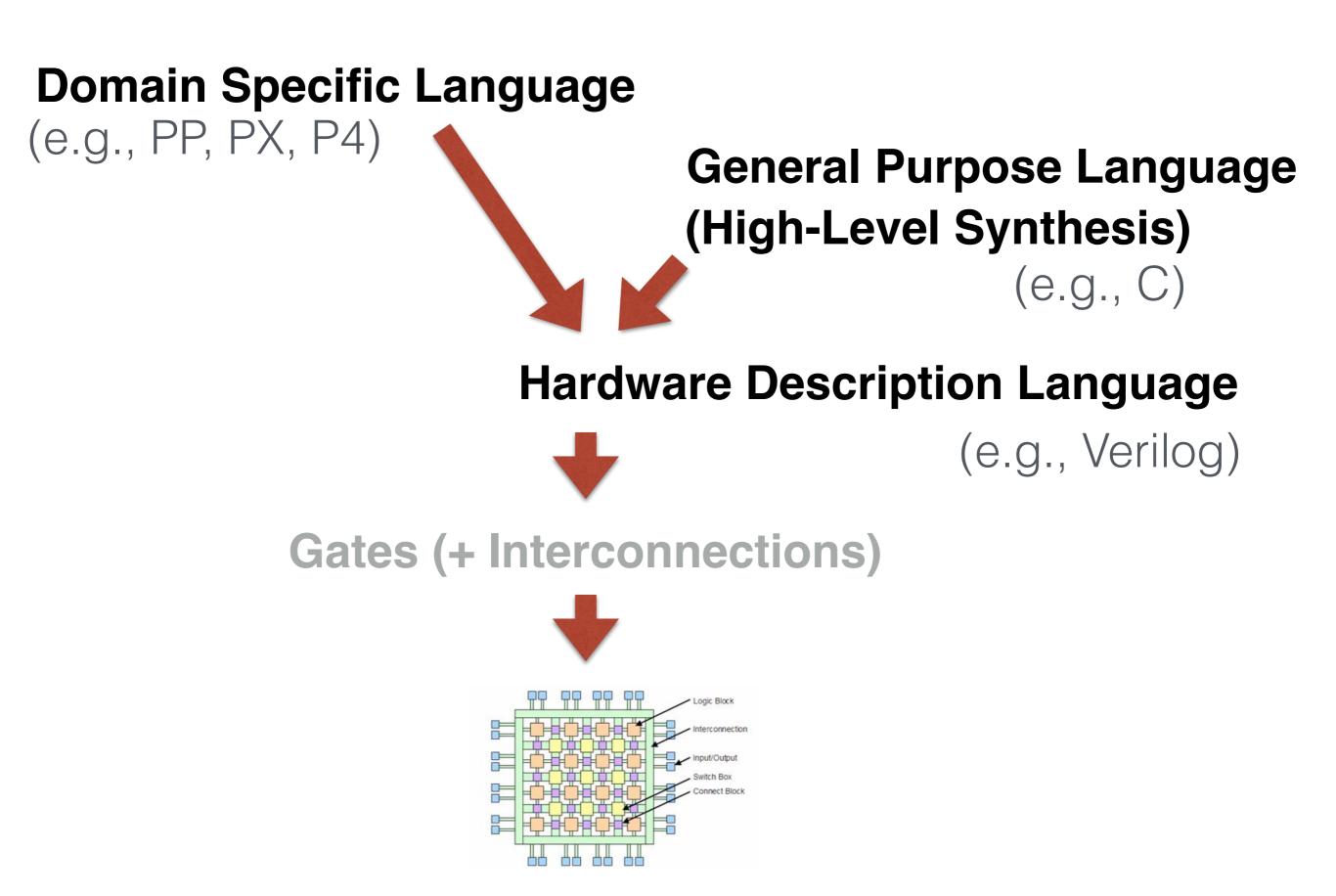

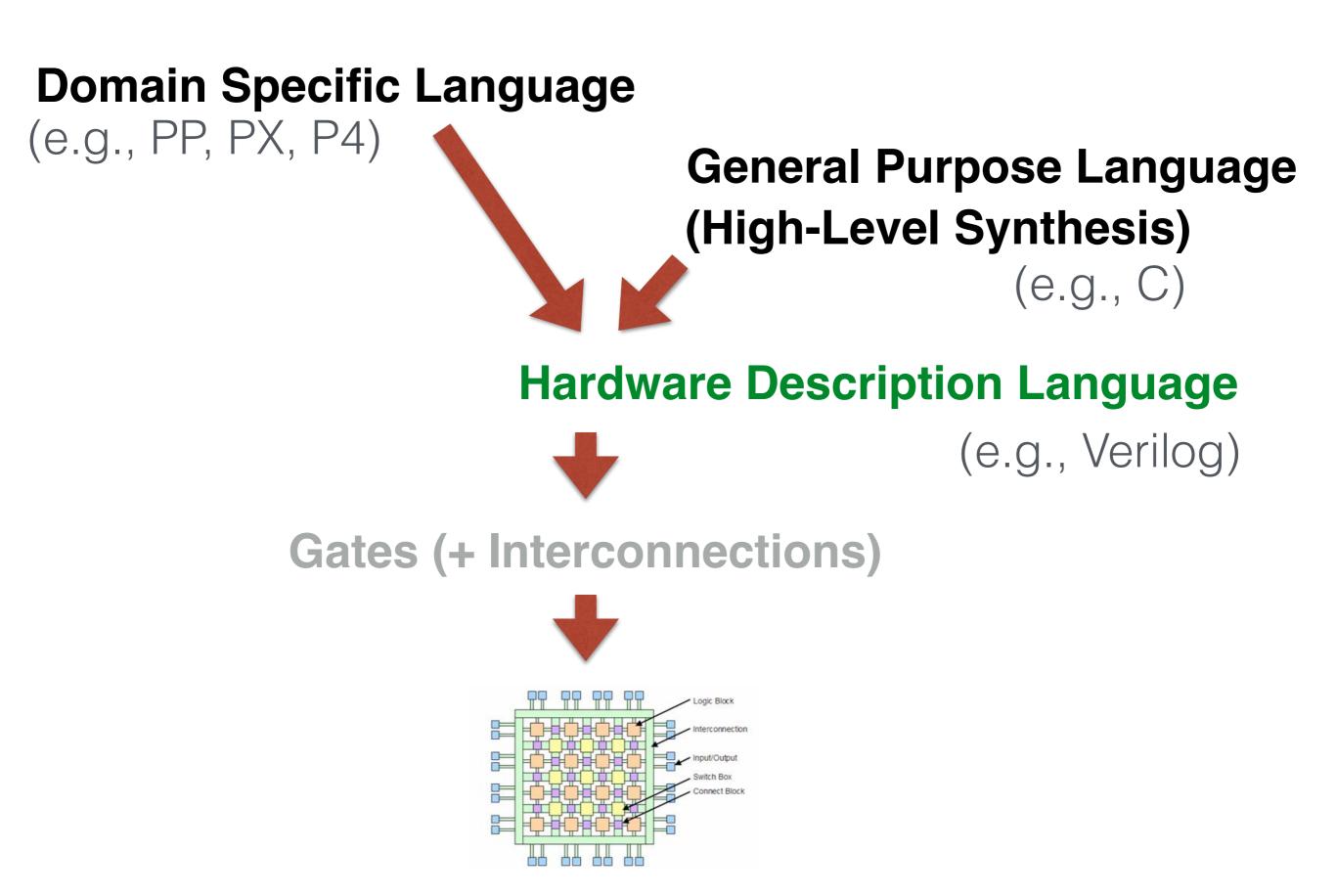

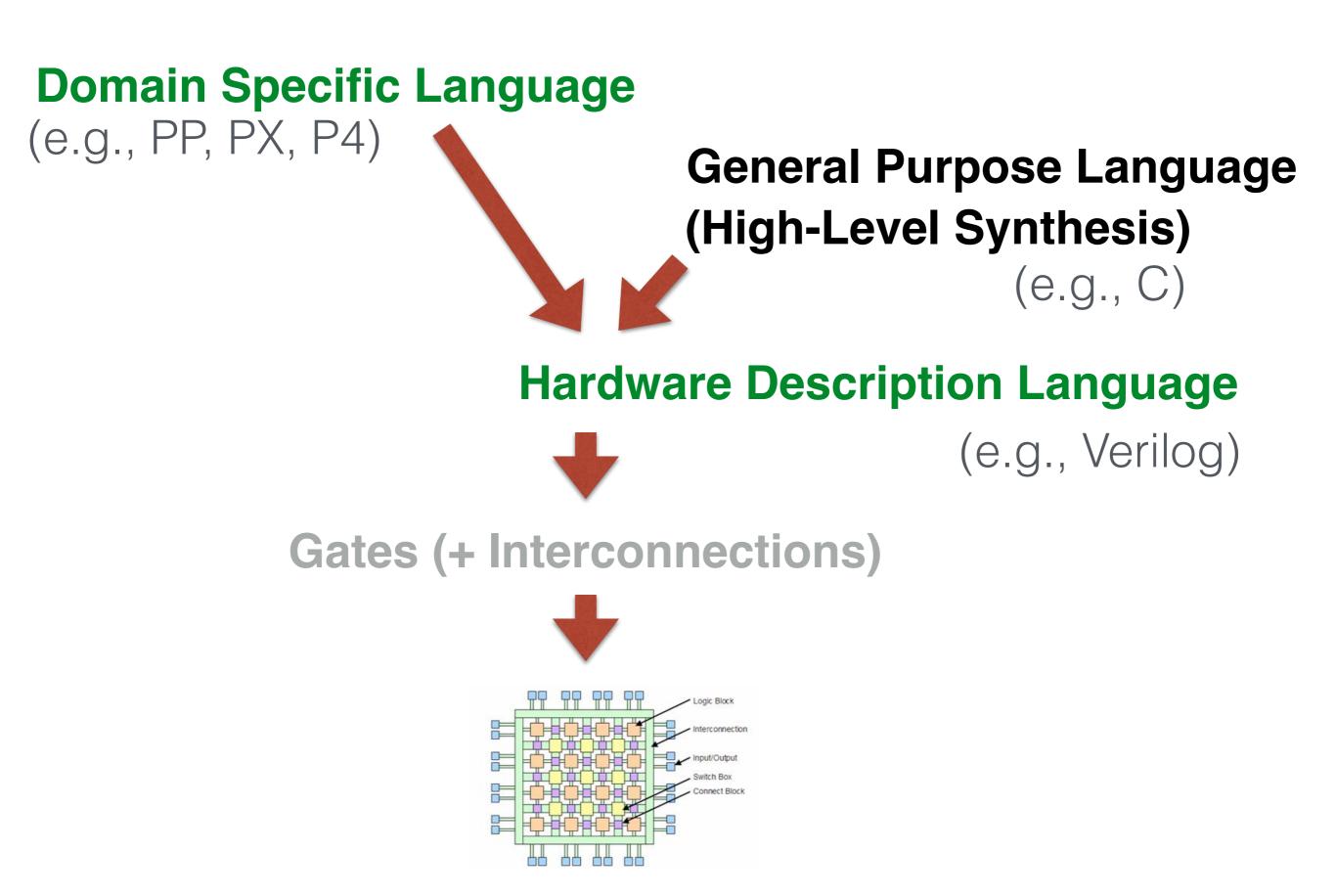

#### **Gates (+ Interconnections)**

### Hardware Description Language

- Lots of **flexibility**.

- How you think code will behave vs how it's translated vs how it executes/implements.

- "reg" ~ register

- "inference"

- "technology mapping"

```

struct node {

unsigned int prev_node : IDX_WIDTH;

unsigned int next_node : IDX_WIDTH;

unsigned int data : DATA_WIDTH;

}

```

struct node memory [MAX\_DEPTH\_IDX+1];

reg [`PREV NODE F MSB:`DATA F LSB] memory [MAX DEPTH IDX:0];

`define PREV\_NODE\_F\_LSB (`NEXT\_NODE\_F\_MSB + 1)

`define PREV\_NODE\_F\_MSB (`PREV\_NODE\_F\_LSB + IDX\_WIDTH - 1)

`define PREV\_NODE F\_WORD\_`PREV\_NODE F\_MSB:`PREV\_NODE F\_LSB

`define NEXT\_NODE\_F\_LSB (`DATA\_F\_MSB + 1)

`define NEXT\_NODE\_F\_MSB (`NEXT\_NODE\_F\_LSB + IDX\_WIDTH - 1)

`define NEXT NODE F WORD `NEXT NODE F MSB:`NEXT NODE F LSB

`define DATA\_F\_LSB 0 `define DATA\_F\_MSB (`DATA\_F\_LSB + DATA\_WIDTH - 1) `define DATA F WORD `DATA F MSB:`DATA F LSB

### Domain-Specific Language

- Much less flexibility. Must stay within "domain".

- Can achieve good performance and more development support (e.g., richer types), and shorter cycles of development.

- **Tuning** can be tricky e.g., breakout to HDL.

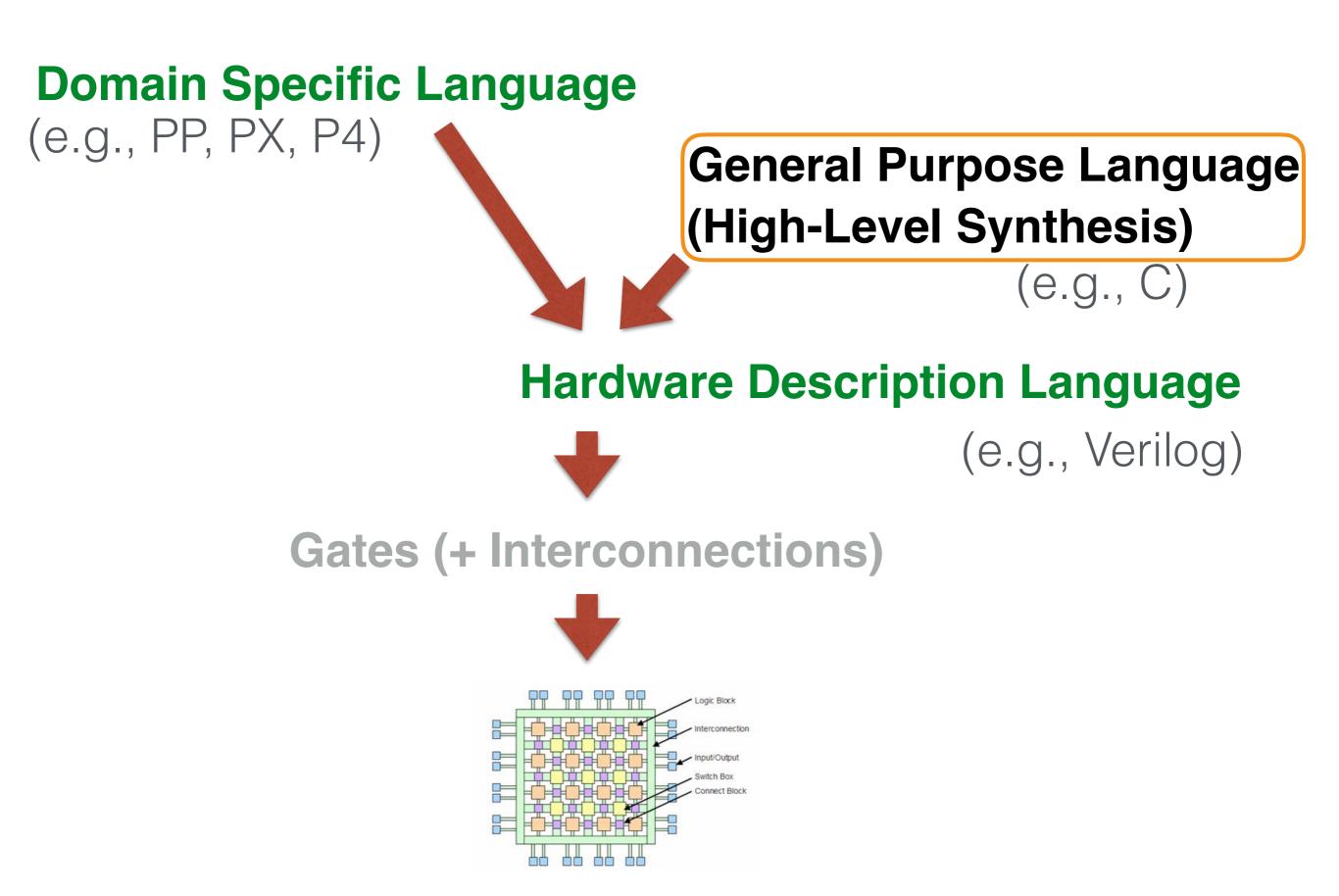

# High-Level Synthesis

- Use "familiar" language.

- Usually **not the full language**. e.g., dynamic allocation only partly supported.

- Often involves library support and language extensions.

- **Tuning** can be tricky e.g., breakout to HDL.

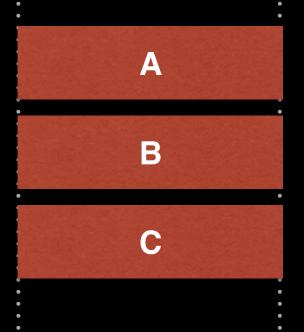

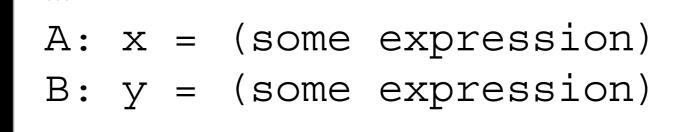

A: x = (some expression) B: y = (some expression) A: x = (some expression) B: y = (some expression)

```

A: x = (some expression)

C: f(x)

B: y = (some expression)

```

A: x = (some expression) C: f(x) B: y = (some expression)

A C B

A: x = (some expression) B: y = (**v.cplx** expression)

A

B

A: x = (some expression) B: y = (some expression)

AB.2

A B.1 B.2 A: x = (some expression) B: y = (some expression)

| <b>B.2</b> | A |

|------------|---|

| <b>B.1</b> |   |

|            |   |

|            |   |

|            |   |

"The user can control how aggressively Stratus HLS packs these operations into each clock period. Creating designs with Stratus HLS can save months of backend effort by preventing timing closure problems."

# cādence®

https://www.cadence.com/content/dam/cadence-www/global/en\_US/documents/tools/digital-design-signoff/stratus-ds.pdf

#### High-level development and debugging of FPGA-based network programs

### ...using HLS

### It won't work...

# It won't work...

#### Performance will suck!

Use HDL modules from HLL for resource-related IP.

# It won't work...

- **Performance will suck!** Use HDL modules from HLL for resource-related IP.

- HLS tools are expensive and closed-source.

Various academic tools exist.

#### It won't work...

- **Performance will suck!** Use HDL modules from HLL for resource-related IP.

- HLS tools are expensive and closed-source. Various academic tools exist.

- Not sufficiently expressive. Can be fixed. (With ingenuity.)

#### It won't work...

- **Performance will suck!** Use HDL modules from HLL for resource-related IP.

- HLS tools are expensive and closed-source. Various academic tools exist.

- Not sufficiently expressive. Can be fixed. (With ingenuity.)

- How to run this in software? Create emulation environment + shadow library.

#### Concerns

Providing benefits for hardware people: improved time-to-market, prototyping, development support, debugging, can breakout to HDL.

#### Concerns

- Providing benefits for hardware people: improved time-to-market, prototyping, development support, debugging, can breakout to HDL.

- Providing benefits for **non-hardware people**: through less steep learning curve, software-like development mindset.

#### Concerns

- Providing benefits for hardware people: improved time-to-market, prototyping, development support, debugging, can breakout to HDL.

- Providing benefits for non-hardware people: through less steep learning curve, software-like development mindset.

- Comparable or better **performance** (latency +throughput) or resource **utilisation** to handwritten HDL.

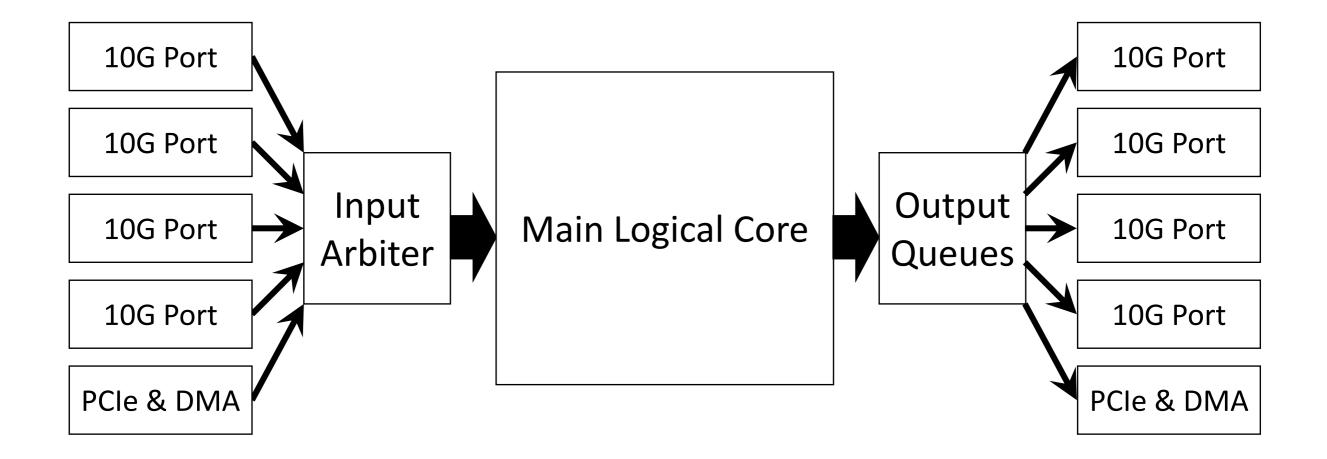

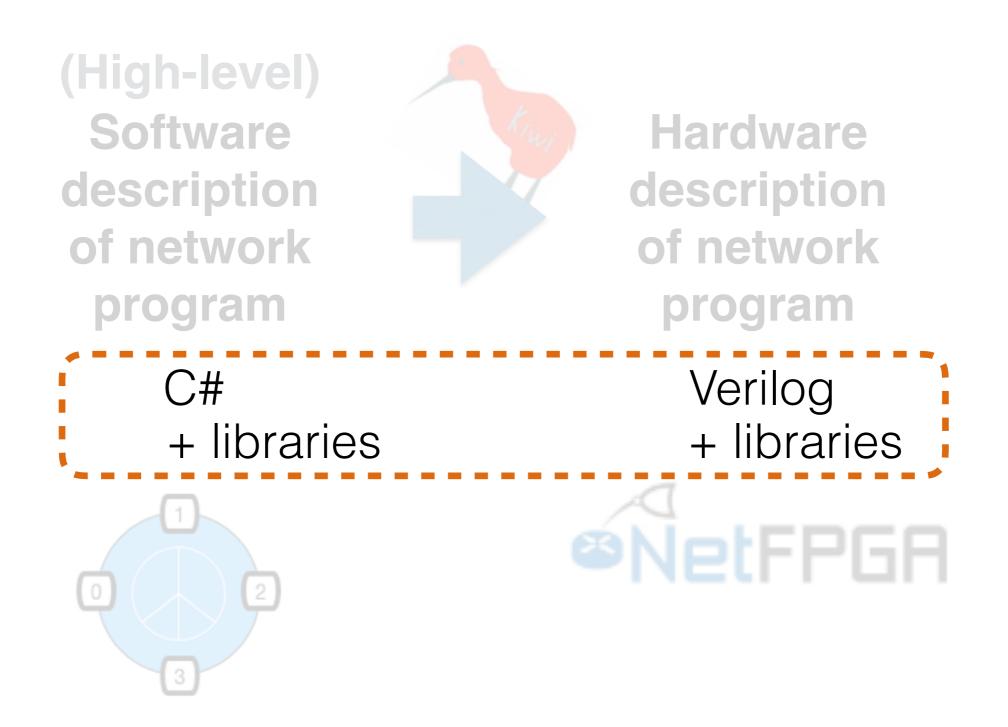

#### Our system: Emu

(High-level) Software description of network program

Hardware description of network program

## (1) HLS

(High-level) Software description of network program

C#

Hardware description of network program Verilog

#### http://www.cl.cam.ac.uk/~djg11/kiwi/

```

public class Data {

public bool matched = false;

public ulong result = 0;

}

public class LRU

Ł

public static Data Lookup(ulong key_in)

Ł

Data res = new Data();

ulong idx = HashCAM.Read(key_in);

if (HashCAM.matched) {

res.matched = HashCAM.matched;

res.result = NaughtyQ.Read(idx);

NaughtyQ.BackOfQ(idx);

}

return res;

}

public static void Cache(ulong key_in, ulong value_in)

{

ulong idx = NaughtyQ.Enlist(value_in);

HashCAM.Write(key_in, idx);

}

}

```

# (2) Library support

(High-level) Software description of network program

Hardware description of network program

C# + libraries Verilog + libraries

### (3) Host environment

(High-level) Software description of network program

Hardware description of network program

Verilog

+ libraries

C# + libraries

#### http://github.com/niksu/Pax

```

private ForwardingDecision OutsideToInside(TEncapsulation packet)

{

// Retrieve the mapping. If a mapping doesn't exist, then it means that we're not

// aware of a session to which the packet belongs: so drop the packet.

var key = new ConnectionKey(packet.GetSourceNode(), packet.GetDestinationNode());

NatConnection<TPacket,TNode> connection;

if (NAT_MapToInside.TryGetValue(key, out connection))

{

var destination = connection TesideNede;

}

}

```

```

var destination = connection.InsideNode;

```

// Update any connection state, including resetting the inactivity timer connection.ReceivedPacket(packet, packetFromInside: false);

```

// Rewrite the packet destination

packet.SetDestination(destination);

```

```

// Update checksums

packet.UpdateChecksums();

```

}

```

// Forward on the mapped network port

return new ForwardingDecision.SinglePortForward(destination.InterfaceNumber);

}

else

{

return Drop;

}

```

#### (3) Hardware envir.

(High-level) Software description of network program

Hardware description of network program

C# + libraries

Verilog + libraries

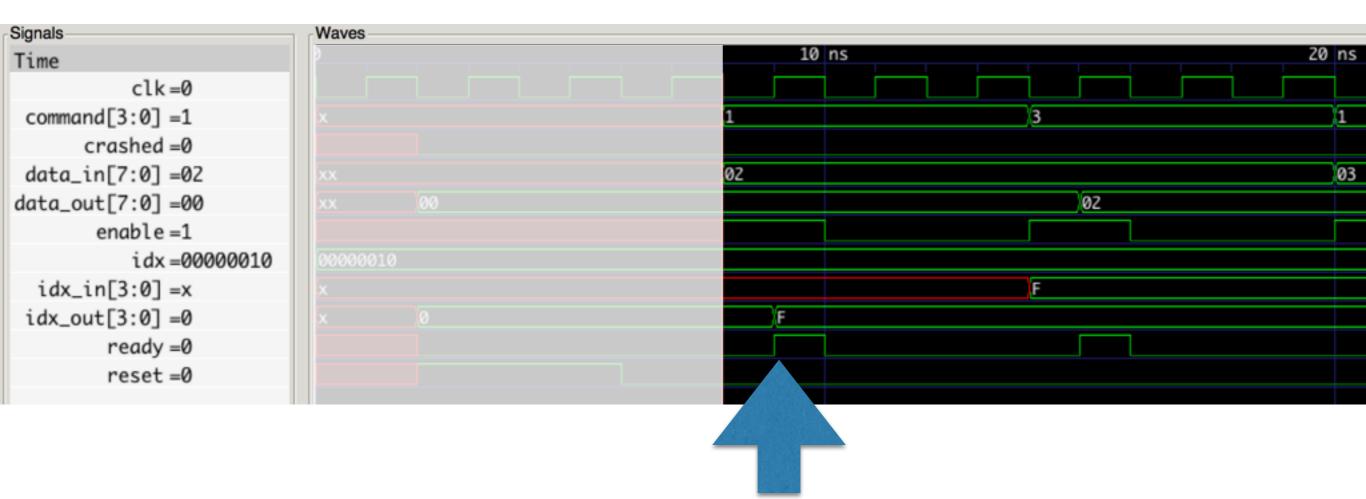

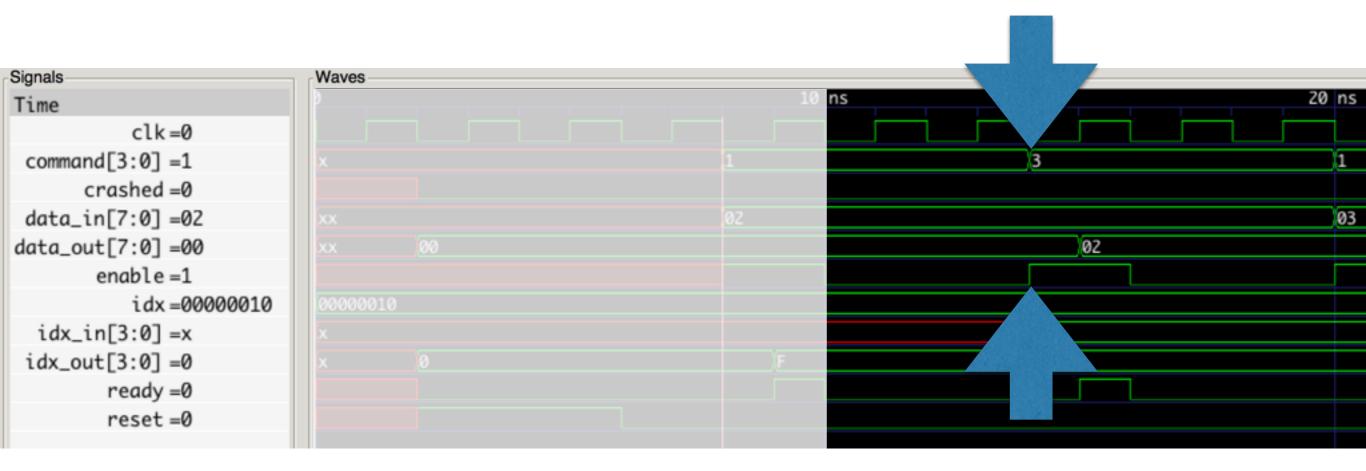

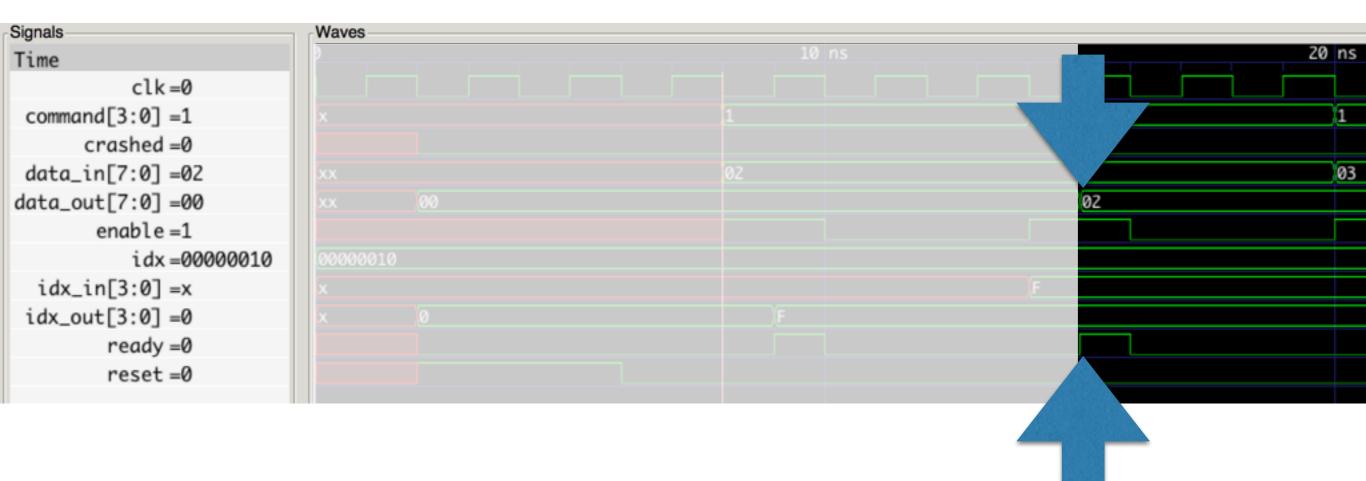

# Lifting & shadowing

```

[Kiwi.OutputBitPort("NQ_enable")]

protected static bool enable;

[Kiwi.InputBitPort("NQ_ready")]

protected static bool ready;

[Kiwi.InputBitPort("NQ_crashed")]

protected static bool crashed;

[Kiwi.OutputWordPort(3, 0, "NQ_command")]

protected static byte command;

[Kiwi.InputWordPort(3, 0, "NQ_idx_out")]

protected static ulong idx_out;

[Kiwi.InputWordPort(7, 0, "NQ_data_out")]

protected static ulong data_out;

[Kiwi.OutputWordPort(3, 0, "NQ_idx_in")]

protected static ulong idx_in;

[Kiwi.OutputWordPort(7, 0, "NQ_data_in")]

protected static ulong data_in;

// Nonvolatile copies of outputs.

public static ulong idx_out_nv;

public static ulong data_out_nv;

public static ulong Enlist(ulong data_in)

Ł

while (ready) { Kiwi.Pause(); }

command = (byte)op_code.Enlist;

NaughtyQ.data_in = data_in;

enable = true;

Kiwi.Pause();

while (!ready) { Kiwi.Pause(); }

Kiwi.Pause();

idx_out_nv = idx_out;

data_out_nv = data_out;

enable = false;

Kiwi.Pause();

return idx_out_nv;

}

```

[Kiwi.OutputBitPort("NQ\_enable")]

protected static bool enable;

[Kiwi.InputBitPort("NQ\_ready")]

protected static bool ready;

[Kiwi.InputBitPort("NQ\_crashed")]

protected static bool crashed;

[Kiwi.OutputWordPort(3, 0, "NQ\_command")]

protected static byte command;

[Kiwi.InputWordPort(3, 0, "NQ\_idx\_out")]

protected static ulong idx\_out;

[Kiwi.InputWordPort(7, 0, "NQ\_data\_out")]

protected static ulong data\_out;

[Kiwi.OutputWordPort(3, 0, "NQ\_idx\_in")]

protected static ulong idx\_in;

[Kiwi.OutputWordPort(7, 0, "NQ\_data\_in")]

protected static ulong data\_in;

// Nonvolatile copies of outputs.

public static ulong idx\_out\_nv;

public static ulong data\_out\_nv;

```

public static ulong Enlist(ulong data_in)

{

while (ready) { Kiwi.Pause(); }

command = (byte)op_code.Enlist;

NaughtyQ.data_in = data_in;

enable = true;

Kiwi.Pause();

while (!ready) { Kiwi.Pause(); }

Kiwi.Pause();

idx_out_nv = idx_out;

data_out_nv = data_out;

enable = false;

Kiwi.Pause();

return idx_out_nv;

}

```

```

public static ulong Enlist(ulong data_in)

ł

while (ready) { Kiwi.Pause(); }

command = (byte)op_code.Enlist;

NaughtyQ.data_in = data_in;

enable = true;

Kiwi.Pause();

while (!ready) { Kiwi.Pause(); }

Kiwi.Pause();

idx_out_nv = idx_out;

data_out_nv = data_out;

enable = false;

Kiwi.Pause();

return idx_out_nv;

}

```

# public static ulong Enlist(ulong data\_in) { while (ready) { Kiwi.Pause(); }

}

```

command = (byte)op_code.Enlist;

NaughtyQ.data_in = data_in;

enable = true;

Kiwi.Pause();

while (!ready) { Kiwi.Pause(); }

Kiwi.Pause();

idx_out_nv = idx_out;

data_out_nv = data_out;

enable = false;

Kiwi.Pause();

return idx_out_nv;

```

#### public static ulong Enlist(ulong data\_in) { while (ready) { Kiwi.Pause(); } command = (byte)op\_code.Enlist; NaughtyQ.data\_in = data\_in; enable = true; Kiwi.Pause(); while (!ready) { Kiwi.Pause(); } Kiwi.Pause(); $idx_out_nv = idx_out;$ $data_out_nv = data_out;$ enable = false; Kiwi.Pause(); return idx\_out\_nv; }

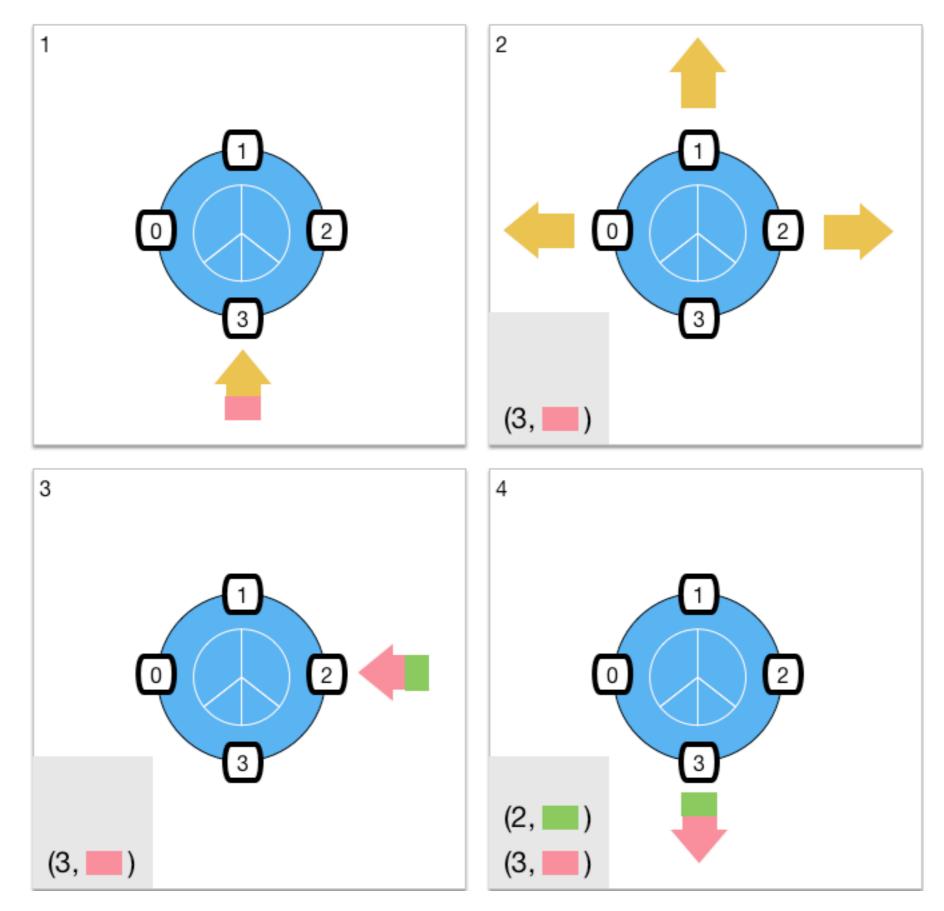

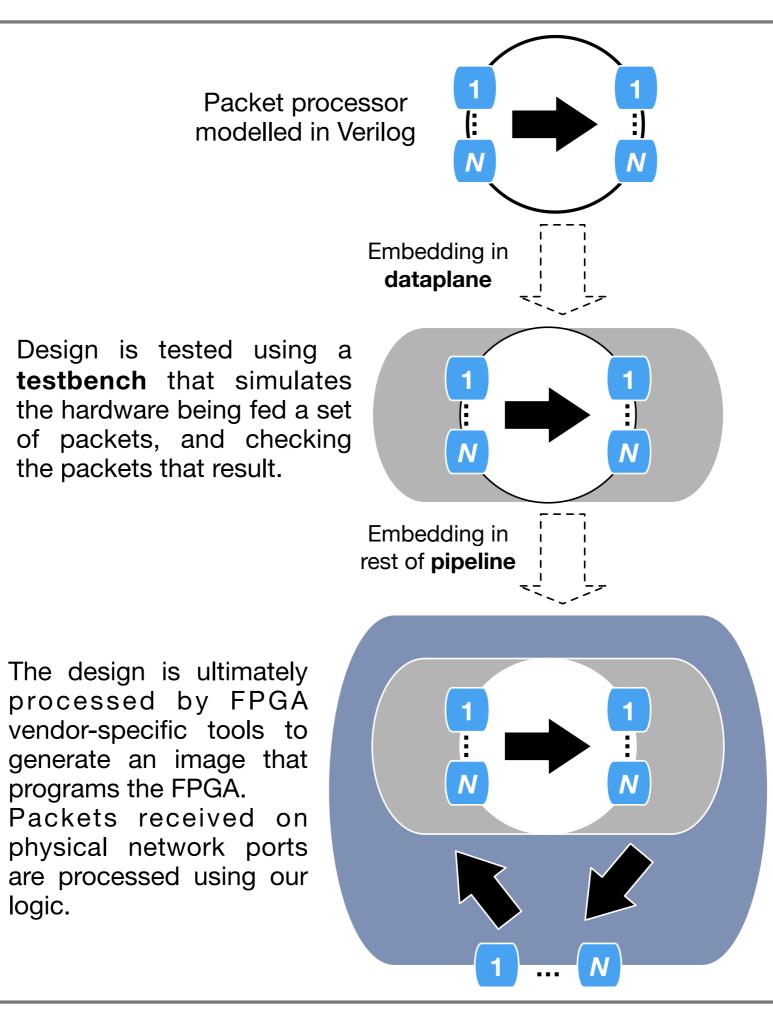

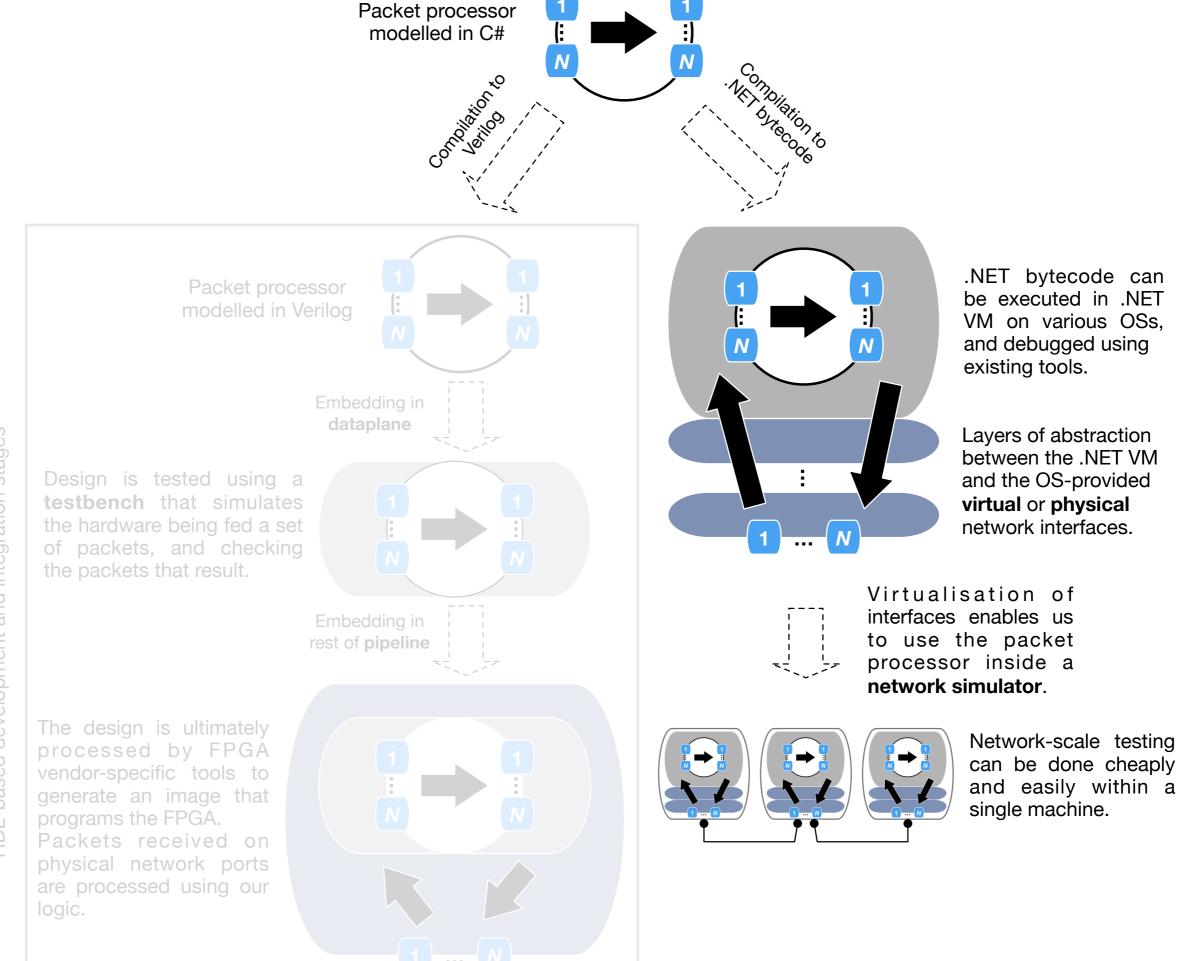

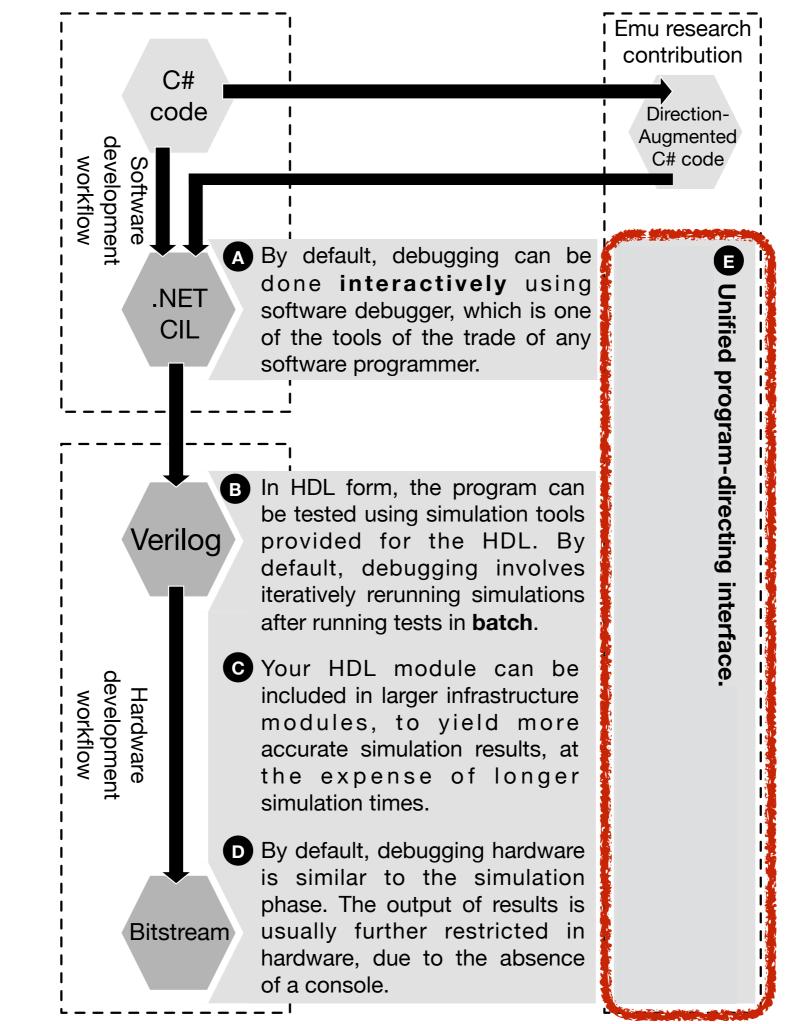

# Workflow

HDL-based development and integration stages

HDL-based development and integration stages

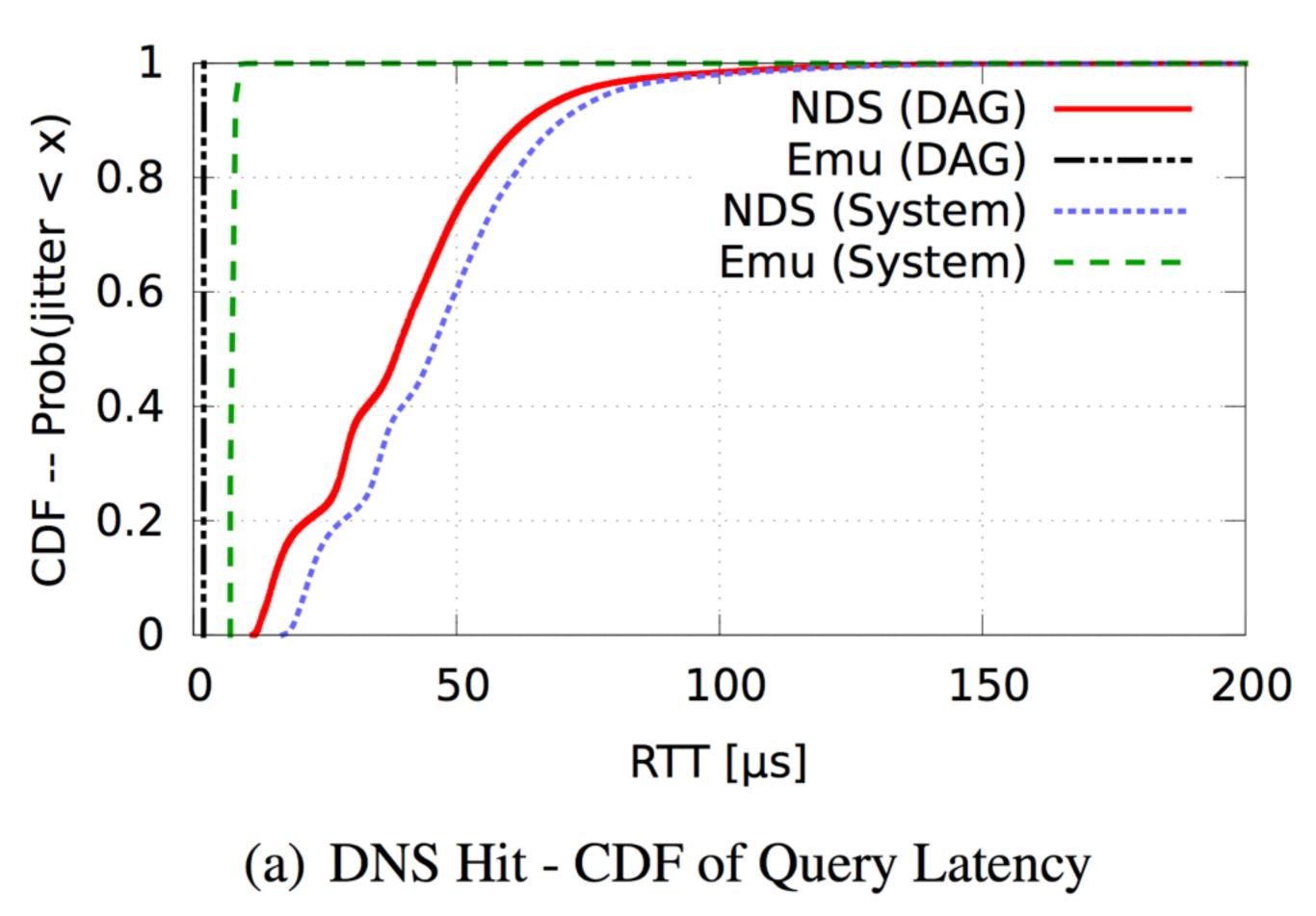

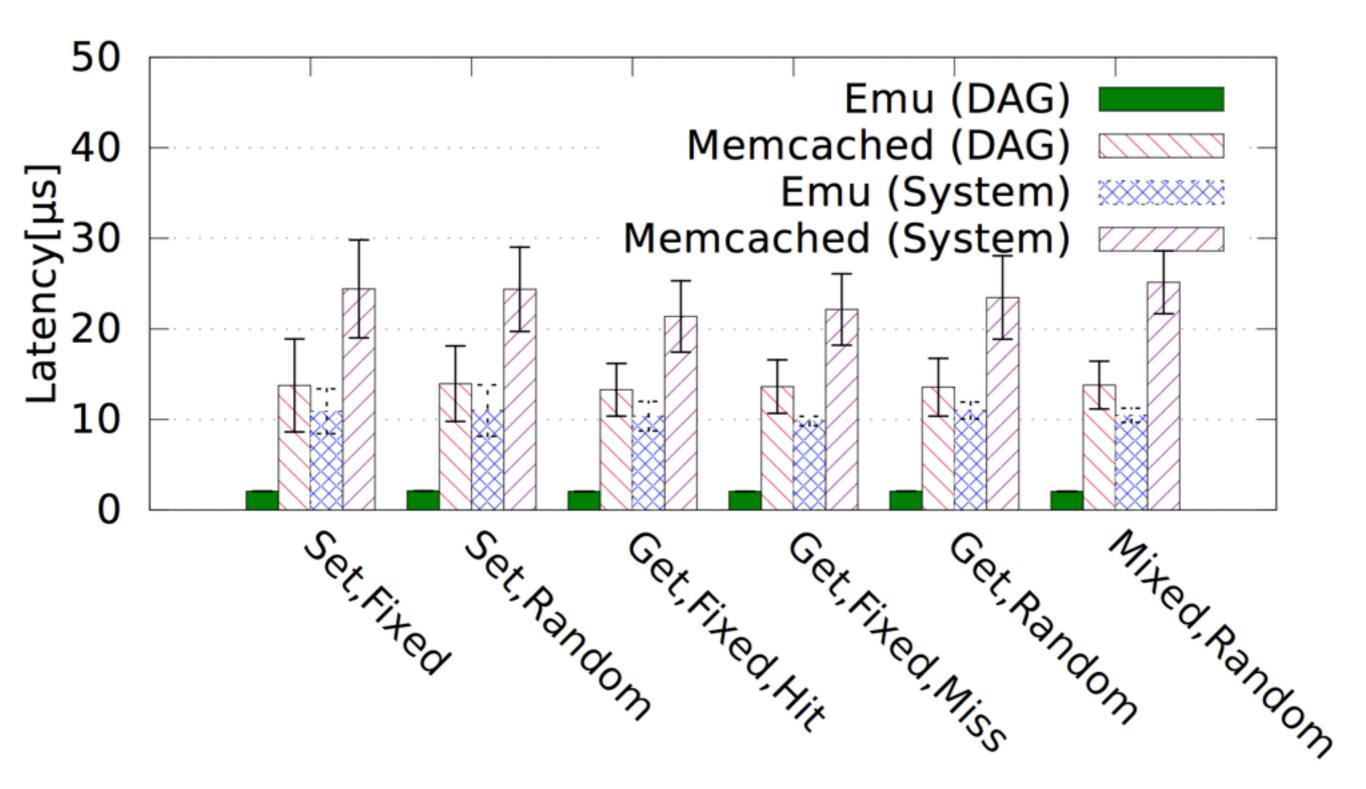

#### Some examples

- Learning switch

- ICMP echo and TCP ping

- DNS

- Memcached

- NAT

#### Some results

| Platform             | <b>Reference Switch</b> | Emu Switch |

|----------------------|-------------------------|------------|

| Logic Utilisation    | 11.42%                  | 12.9 %     |

| Memory Utilisation   | 13.23%                  | 13.5%      |

| Bandwidth            | 32Gbps                  | 32.7Gbps   |

| Port-to-port Latency | 823ns                   | 825ns      |

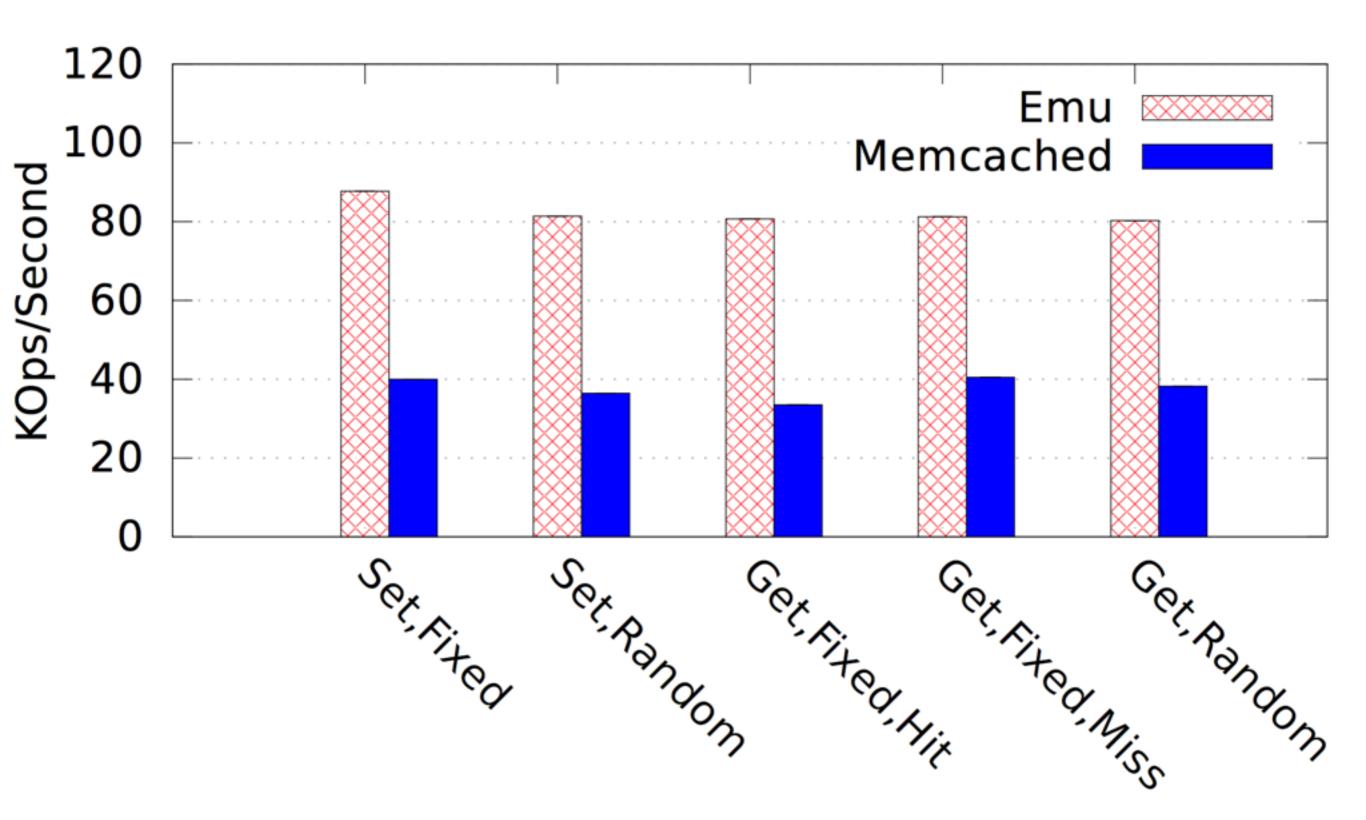

(a) Memcached - Latency

(b) Memcached - Throughput

#### High-level development and debugging of FPGA-based network programs

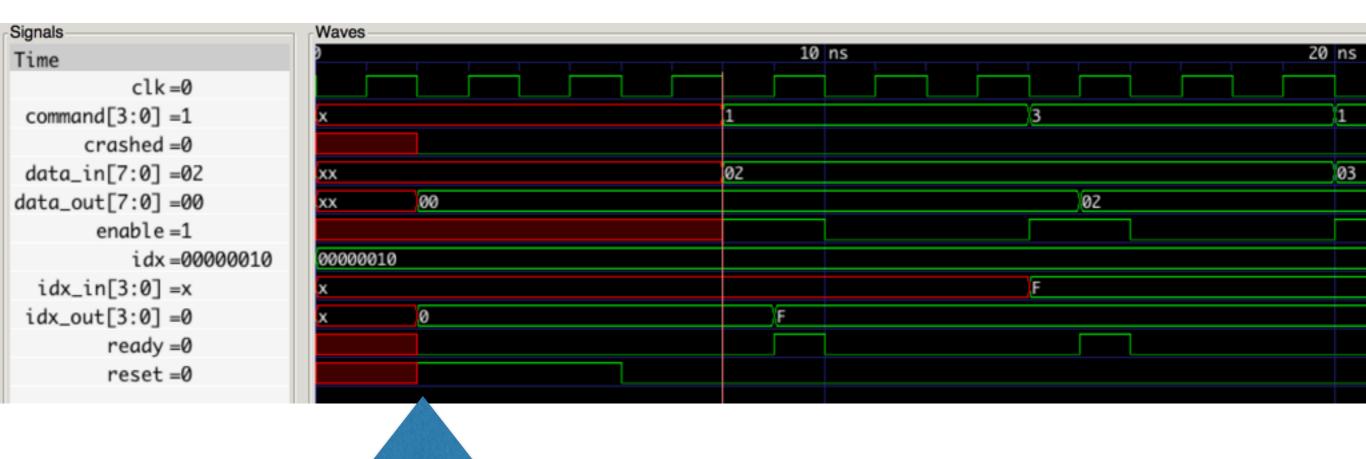

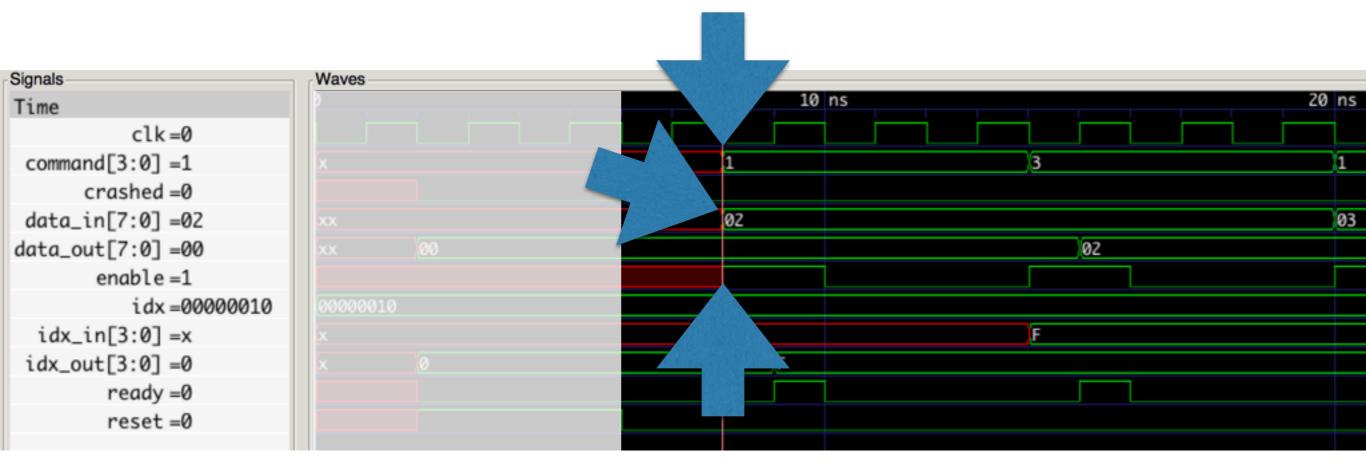

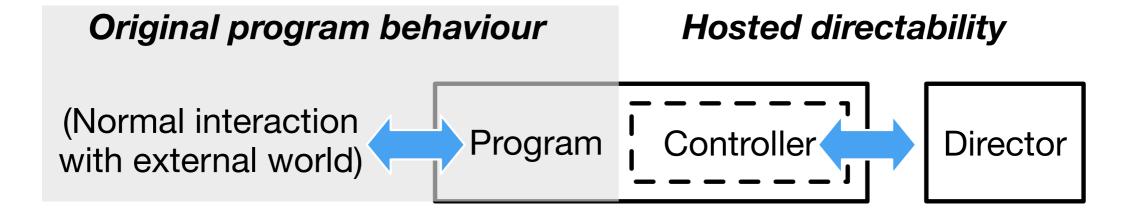

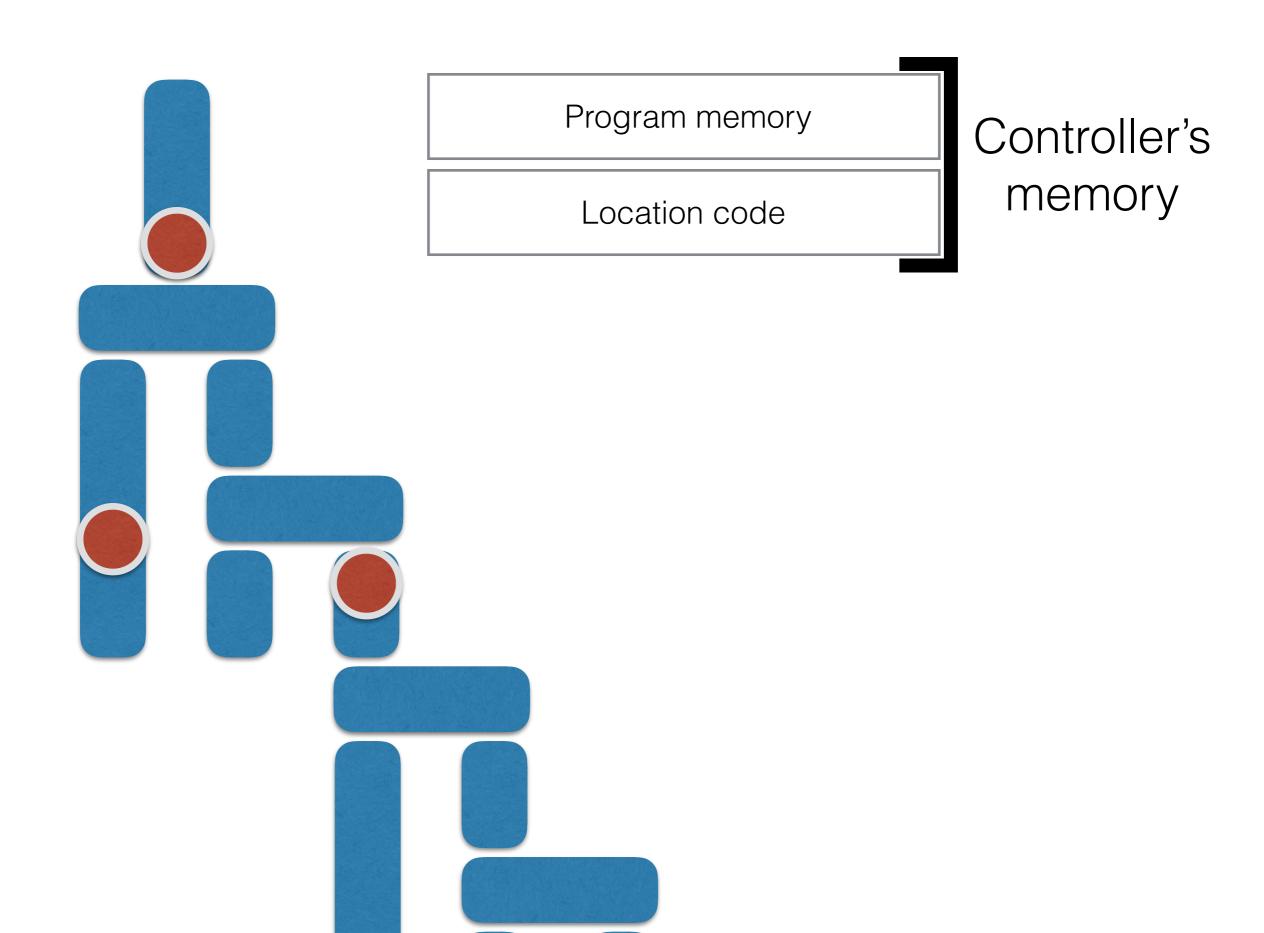

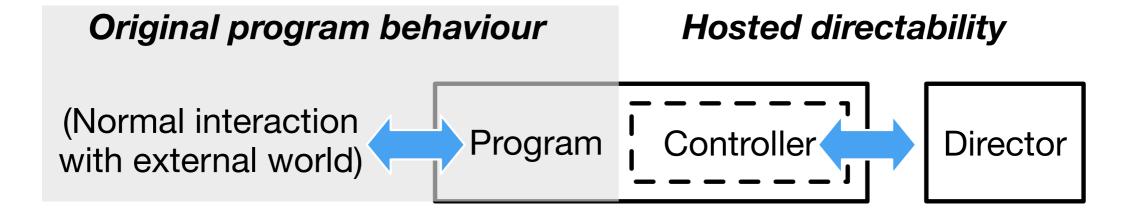

#### "Program-hosted Directability" (PhD)

- Program direction

- PhD: transforming programs to host their own directability features.

- "direction feature" becomes a program in constrained language.

- Can invoke/reconfigure these features at runtime.

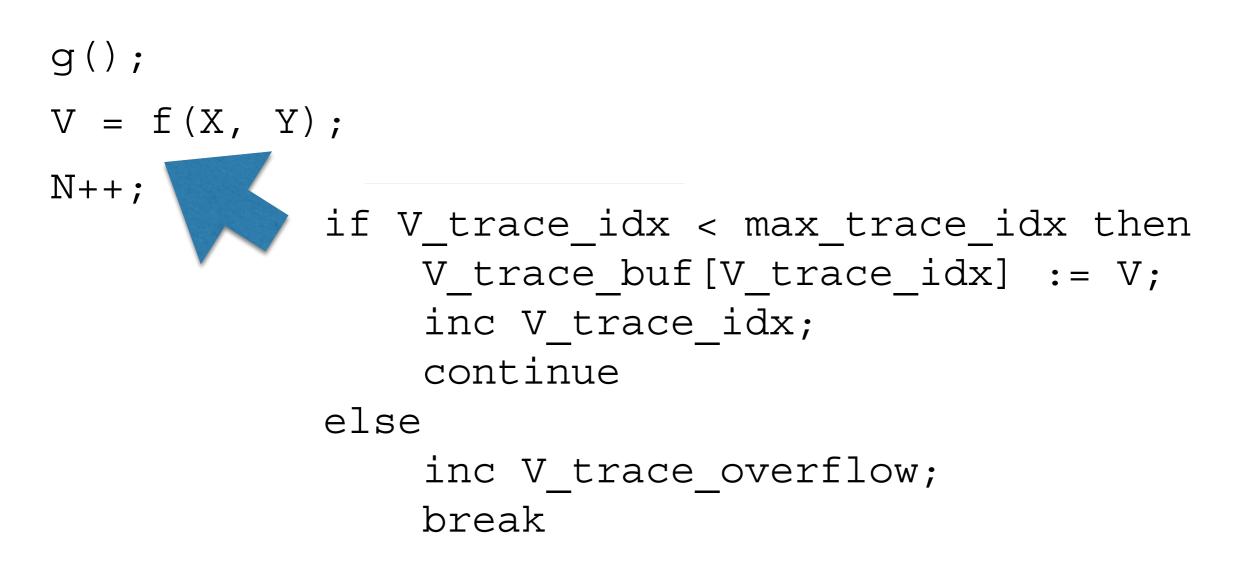

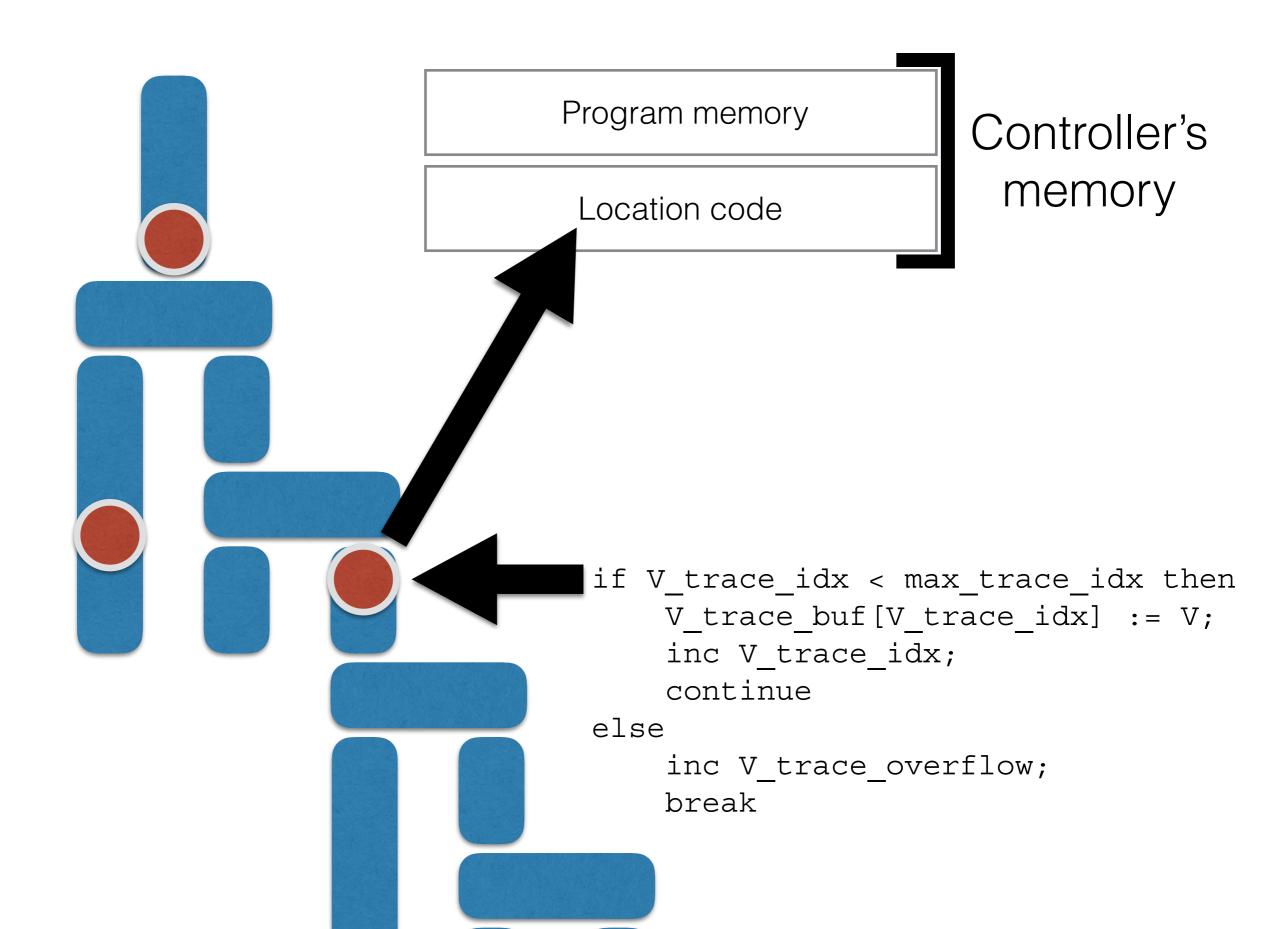

### trace V max\_trace\_idx

g(); V = f(X, Y); N++;

### trace V max\_trace\_idx

| Command                                                                                                                                                                                                                                                                                                                                                                                                | Behaviour                                                                                                          |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| print $X$                                                                                                                                                                                                                                                                                                                                                                                              | Print the value of variable X from the source program.                                                             |  |  |  |  |  |  |  |

| break $L\langle B angle$                                                                                                                                                                                                                                                                                                                                                                               | Activate a (conditional) breakpoint at the position of label L.                                                    |  |  |  |  |  |  |  |

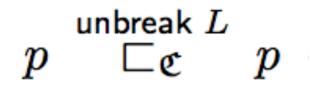

| unbreak $L$                                                                                                                                                                                                                                                                                                                                                                                            | Deactivate a breakpoint.                                                                                           |  |  |  |  |  |  |  |

| backtrace $\langle \$ \rangle$                                                                                                                                                                                                                                                                                                                                                                         | Print the "function call stack".                                                                                   |  |  |  |  |  |  |  |

| watch $X \langle B \rangle$                                                                                                                                                                                                                                                                                                                                                                            | Break when X is updated and satisfies a given condition.                                                           |  |  |  |  |  |  |  |

| unwatch X                                                                                                                                                                                                                                                                                                                                                                                              | Cancel the effect of the "watch" command.                                                                          |  |  |  |  |  |  |  |

| $\left\{\begin{array}{c} \operatorname{reads} X \left\langle B \right\rangle \left\langle \$ \right\rangle \\ \operatorname{writes} X \left\langle B \right\rangle \left\langle \$ \right\rangle \\ \operatorname{calls} fname \left\langle B \right\rangle \left\langle \$ \right\rangle \\ \operatorname{start} X \left\langle B \right\rangle \left\langle \$ \right\rangle \\ \end{array}\right\}$ | Count the reads or writes to a variable $X$ , or the calls to a function <i>fname</i> .                            |  |  |  |  |  |  |  |

| start $X \langle B \rangle \langle \$ \rangle$<br>stop $X$                                                                                                                                                                                                                                                                                                                                             | Trace a variable, subject to a condition being satisfied, and up to trace some length.<br>Stop tracing a variable. |  |  |  |  |  |  |  |

| trace $\begin{cases} \text{stop } X \\ \text{clear } X \end{cases}$                                                                                                                                                                                                                                                                                                                                    | Clear a variable's trace buffer.                                                                                   |  |  |  |  |  |  |  |

| print $X$                                                                                                                                                                                                                                                                                                                                                                                              | Print the contents of a variable's trace buffer.                                                                   |  |  |  |  |  |  |  |

| full X                                                                                                                                                                                                                                                                                                                                                                                                 | Check if a variable's trace buffer is full.                                                                        |  |  |  |  |  |  |  |

**Table 2.** Directing commands making up language  $\mathfrak{D}$ . Note that count has similar subcommands to those of trace, to clear the counters, get their current value, and find out if a maximum value has been reached.

| Artefact                     | Utilisa                    | ation (%)                  | Performance           |                      |                               |  |  |  |  |  |

|------------------------------|----------------------------|----------------------------|-----------------------|----------------------|-------------------------------|--|--|--|--|--|

|                              | Logic                      | Flip-flops                 | Duration<br>(#cycles) | -                    | Queries-<br>per-sec<br>(KQPS) |  |  |  |  |  |

| DNS+ELA                      | 99.74                      | 100.40                     | 57                    | 1.83                 | 1176                          |  |  |  |  |  |

| DNS+2e<br>(Count)<br>(Trace) | 234.61<br>234.46<br>218.30 | 151.06<br>151.81<br>151.84 | 57<br>62<br>70        | 1.86<br>1.94<br>1.99 | 1176<br>1064<br>1010          |  |  |  |  |  |

**Table 4.** Utilisation and performance profile of the DNS+ELA against the DNS having one extension point, where the extension point is NOP, packet counting, or variable tracing. Latency is indicated at the  $99^{th}$  percentile.

| sənnres<br>System                   | state inspection | trace recording | state updating | extension points | break points | stepping     | interruption | fine granularity | assertion checking | hang detection | timing checks | software instance | runtime reconfigurable | HLS (vs HDL) | Network/Control | use leftover resource | embed at Source/HDL |

|-------------------------------------|------------------|-----------------|----------------|------------------|--------------|--------------|--------------|------------------|--------------------|----------------|---------------|-------------------|------------------------|--------------|-----------------|-----------------------|---------------------|

| (Sosič 1992) Dynascope              | ✓                | $\checkmark$    | ✓              | $\checkmark$     | $\checkmark$ | ✓            | $\checkmark$ | $\checkmark$     | $\checkmark$       |                |               | ✓                 | ✓                      |              |                 |                       |                     |

| (Goeders and Wilton 2014) HLS-Scope | $\checkmark$     | $\checkmark$    |                |                  | $\checkmark$ | $\checkmark$ |              | $\checkmark$     |                    |                |               |                   |                        | $\checkmark$ | C               |                       | S                   |

| (Calagar et al. 2014) Inspect       | $\checkmark$     |                 |                |                  | $\checkmark$ | $\checkmark$ |              | $\checkmark$     |                    |                |               | $\checkmark$      |                        | $\checkmark$ | С               |                       | Η                   |

| (Panjkov et al. 2015)               | $\checkmark$     |                 |                |                  |              |              |              |                  |                    |                |               |                   |                        | $\checkmark$ | C               |                       | S                   |

| (Hung and Wilton 2014) QuickTrace   | $\checkmark$     |                 |                |                  |              |              |              | $\checkmark$     |                    |                |               | $\checkmark$      | $\checkmark$           | $\checkmark$ | Ν               | $\checkmark$          | Η                   |

| (Koch et al. 1998) SLE/CADDY        | $\checkmark$     |                 |                |                  | $\checkmark$ | $\checkmark$ |              | $\checkmark$     |                    |                |               | $\checkmark$      |                        | $\checkmark$ | C               |                       | Н                   |

| (Monson and Hutchings 2015)         | $\checkmark$     | $\checkmark$    |                |                  |              |              |              |                  |                    |                |               |                   |                        | $\checkmark$ | С               |                       | S                   |

| (Curreri et al. 2011)               |                  |                 |                |                  |              |              |              |                  | $\checkmark$       | $\checkmark$   | $\checkmark$  |                   |                        | $\checkmark$ | C               |                       | Н                   |

| (Camera et al. 2005) BORPH          | $\checkmark$     | $\checkmark$    | $\checkmark$   |                  | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$     |                    |                |               |                   |                        |              | C               |                       | Η                   |

| (see §2.5) PhD                      | $\checkmark$     | $\checkmark$    | $\checkmark$   | $\checkmark$     | $\checkmark$ |              | $\checkmark$ | $\checkmark$     | $\checkmark$       |                |               | $\checkmark$      | $\checkmark$           |              | C               |                       |                     |

Table 1. Survey of features provided by debugging systems. Blacked-out boxes mean "not applicable".

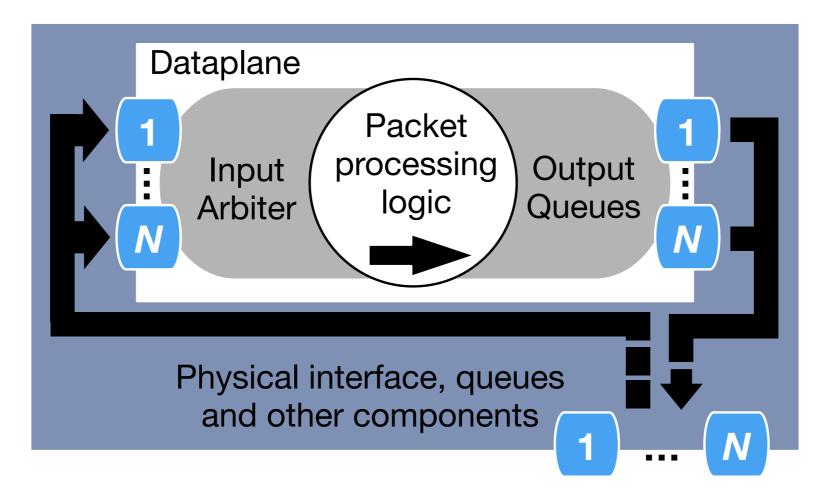

• Goal: HLS-based development of network programs

- Goal: HLS-based development of network programs

- **Currently**: done using HDL or DSL. We use HLS.

- Goal: HLS-based development of network programs

- **Currently**: done using HDL or DSL. We use HLS.

- What's new: lifting+shadowing, host support environment, improved debugging support.

- Goal: HLS-based development of network programs

- **Currently**: done using HDL or DSL. We use HLS.

- What's new: lifting+shadowing, host support environment, improved debugging support.

- **Relevance**: will help experienced and novice users of FPGAs, at a time when FPGAs becoming more prevalent.

# Thank you

naas-project.org

## Extra slides

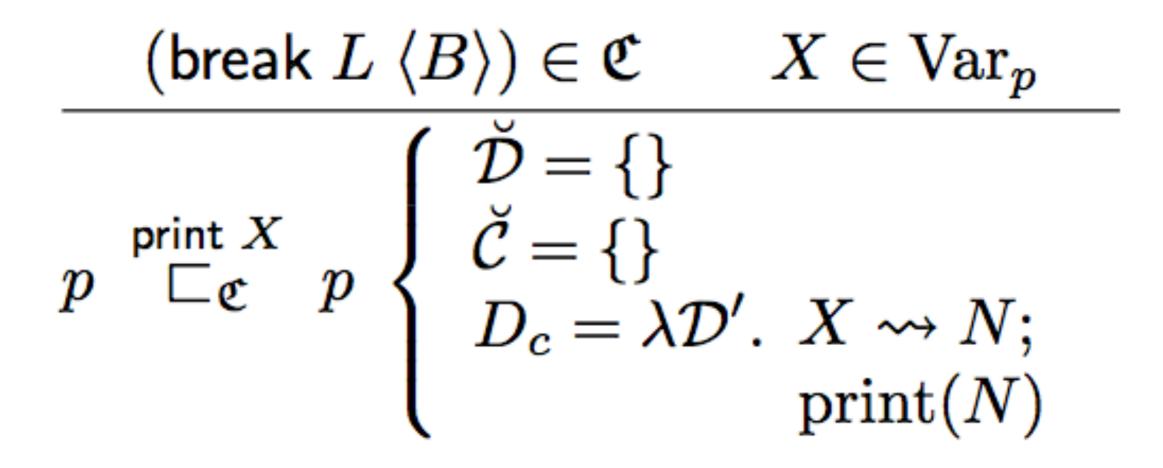

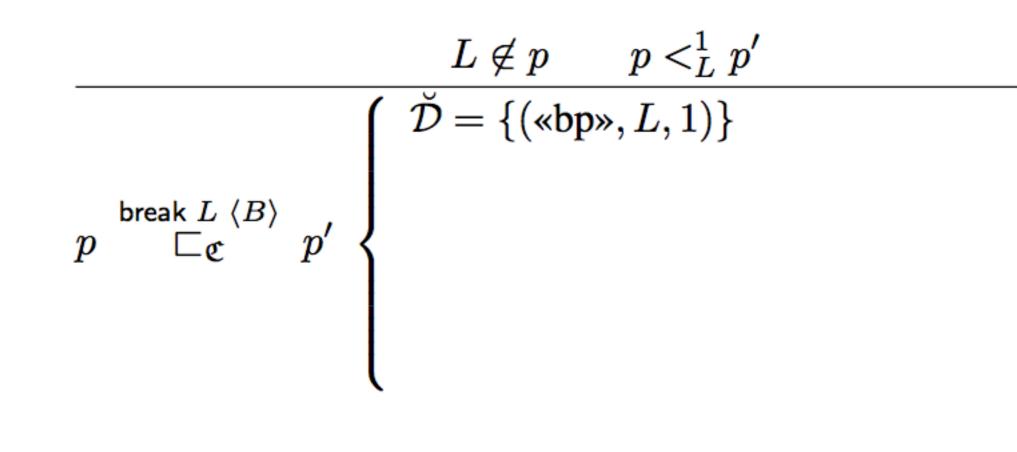

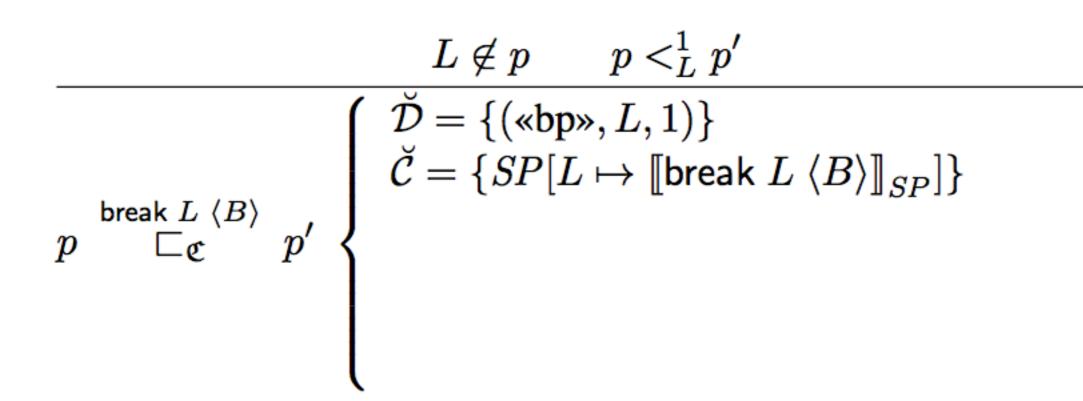

# Three examples:

- print

- break

- unbreak

## $(\mathsf{break}\ L\ \langle B \rangle) \in \mathfrak{C} \qquad X \in \mathrm{Var}_p$

### $(\mathsf{break}\ L\ \langle B \rangle) \in \mathfrak{C} \qquad X \in \mathrm{Var}_p$

$p \quad \Box \mathfrak{C} \quad p$  (need differentiating criteria)

$$\begin{array}{ll} \operatorname{conditional}\left\langle B\right\rangle t \ = & \\ \begin{cases} t & \quad \text{if}\left\langle B\right\rangle = \operatorname{true} \\ \text{if}\ I_1 == I_2 \ \text{then}\ t & \quad \text{if}\left\langle B\right\rangle = (I_1 = I_2) \\ & \quad \text{else continue} \end{cases}$$

$[\![ break \ L \ \langle B \rangle ]\!]_{SP} = \text{conditional} \ \langle B \rangle \ break$

$\begin{array}{ll} \operatorname{conditional}\left\langle B\right\rangle t \ = \\ \begin{cases} t & \text{if } \langle B\rangle = \operatorname{true} \\ \operatorname{if} I_1 == I_2 \operatorname{then} t & \text{if } \langle B\rangle = (I_1 = I_2) \\ & \text{else continue} \end{cases}$

$$\begin{split} & \llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} = \text{conditional } \langle B \rangle \ \text{break} \\ & \llbracket \text{break } L \ \langle B \rangle \rrbracket = @L : \{ \llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} \} \\ & \text{conditional } \langle B \rangle \ t \ = \\ & \begin{cases} t & \text{if } \langle B \rangle = \text{true} \\ \text{if } I_1 == I_2 \ \text{then } t & \text{if } \langle B \rangle = (I_1 = I_2) \\ & \text{else continue} \end{cases} \end{split}$$

$$p \stackrel{\mathsf{break}\ L\ \langle B

angle}{\sqsubset} p'$$

$$\begin{split} \llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} &= \text{conditional } \langle B \rangle \text{ break} \\ \llbracket \text{break } L \ \langle B \rangle \rrbracket &= @L : \{\llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} \} \\ \text{conditional } \langle B \rangle \ t &= \\ \begin{cases} t & \text{if } \langle B \rangle = \text{true} \\ \text{if } I_1 &== I_2 \text{ then } t & \text{if } \langle B \rangle = (I_1 = I_2) \\ & \text{else continue} \end{cases} \end{split}$$

$$\begin{split} \llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} &= \text{conditional } \langle B \rangle \text{ break} \\ \llbracket \text{break } L \ \langle B \rangle \rrbracket &= @L : \{\llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} \} \\ \text{conditional } \langle B \rangle \ t &= \\ \begin{cases} t & \text{if } \langle B \rangle = \text{true} \\ \text{if } I_1 &== I_2 \text{ then } t & \text{if } \langle B \rangle = (I_1 = I_2) \\ & \text{else continue} \end{cases} \end{split}$$

$$\begin{split} \llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} &= \text{conditional } \langle B \rangle \text{ break} \\ \llbracket \text{break } L \ \langle B \rangle \rrbracket &= @L : \{\llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} \} \\ \text{conditional } \langle B \rangle \ t &= \\ \begin{cases} t & \text{if } \langle B \rangle = \text{true} \\ \text{if } I_1 &== I_2 \text{ then } t & \text{if } \langle B \rangle = (I_1 = I_2) \\ & \text{else continue} \end{cases} \end{split}$$

$$\begin{array}{c|c} L \not\in p & p <_{L}^{1} p' \\ \hline \\ \hline \\ p & \stackrel{\mathsf{break} \ L \ \langle B \rangle}{\sqsubset_{\mathfrak{C}}} p' & \begin{cases} \breve{\mathcal{D}} = \{(\mathsf{«bp} \mathrel{\gg}, L, 1)\} \\ \breve{\mathcal{C}} = \{SP[L \mapsto [\![\mathsf{break} \ L \ \langle B \rangle]\!]_{SP}]\} \\ D_c = \lambda \mathcal{D}'. \text{ if } (\mathsf{«bp} \mathrel{\gg}, L, 1) \in \mathcal{D}' \text{ then } \mathcal{D}' \\ & \text{else} \\ & [\![\mathsf{break} \ L \ \langle B \rangle]\!] \rightsquigarrow \ulcorner L \urcorner; \\ (\mathsf{«bp} \mathrel{\gg}, L, 0 \mapsto 1) : \in \mathcal{D}' \end{cases} \end{array}$$

where

$$\begin{split} & \llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} = \text{conditional } \langle B \rangle \ \text{break} \\ & \llbracket \text{break } L \ \langle B \rangle \rrbracket = @L : \{ \llbracket \text{break } L \ \langle B \rangle \rrbracket_{SP} \} \\ & \text{conditional } \langle B \rangle \ t = \\ & \begin{cases} t & \text{if } \langle B \rangle = \text{true} \\ \text{if } I_1 == I_2 \ \text{then } t & \text{if } \langle B \rangle = (I_1 = I_2) \\ & \text{else continue} \end{cases} \end{split}$$

### $(\mathsf{break}\ L\ \langle B\rangle) \in \mathfrak{C}$

$p \stackrel{\mathsf{unbreak}\ L}{\sqsubset} p$

### $(\mathsf{break}\ L\ \langle B \rangle) \in \mathfrak{C}$

#### $\llbracket unbreak L \rrbracket = @L : \{continue\}$

$$(break \ L \ \langle B \rangle) \in \mathfrak{C}$$

$$p \stackrel{\mathsf{unbreak} \ L}{\sqsubset} p \begin{cases} \breve{\mathcal{D}} = \{\} \\ \breve{\mathcal{C}} = \{\} \\ D_c = \lambda \mathcal{D}'. \text{ if } (\mathsf{\ (\ dp\ \)}, L, 0) \in \mathcal{D}' \text{ then } \mathcal{D}' \\ else \ [\![\mathsf{unbreak} \ L]\!] \rightsquigarrow \ulcorner L\urcorner; \\ (\mathsf{\ (\ dp\ \)}, L, 1 \mapsto 0) :\in \mathcal{D}' \end{cases}$$

where

$[\![\texttt{unbreak}\ L]\!] = @L: \{\texttt{continue}\}$